# Real-Time Systems

# Lecture 9: DC Implementables II

2017-11-28

Dr. Bernd Westphal

Albert-Ludwigs-Universität Freiburg, Germany

#### Content

- Correctness Proof for the Gas Burner Implementables

- Now where's the implementation?

- Programmable Logic Controllers (PLC)

- → How do they look like?

- What's special about them?

- ☐ The read/compute/write cycle of PLC

- Example: Stutter Filter

- Structured Text example

- Other IEC 61131-3 programming languages

- PLC Automata

- **Example**: Stutter Filter

- → PLCA Semantics by example

- └- Cycle time

3 - Scontent -

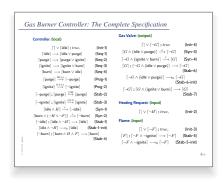

# Gas Burner Controller: The Complete Specification

C: { idle, purge, ignik, bun }

#### Controller: (local)

$\lceil \rceil \lor \lceil \mathsf{idle} \rceil$ ; true, (Init-1)  $\lceil \mathsf{idle} \rceil \longrightarrow \lceil \mathsf{idle} \lor \mathsf{purge} \rceil$ (Seq-1)  $\lceil \mathsf{purge} \rceil \longrightarrow \lceil \mathsf{purge} \lor \mathsf{ignite} \rceil$ (Seq-2)  $\lceil ignite \rceil \longrightarrow \lceil ignite \lor burn \rceil$ (Seq-3)  $\lceil \mathsf{burn} \rceil \longrightarrow \lceil \mathsf{burn} \vee \mathsf{idle} \rceil$ (Seq-4)  $\lceil \mathsf{purge} \rceil \overset{30+\varepsilon}{\longrightarrow} \lceil \neg \mathsf{purge} \rceil$ (Prog-1)  $\lceil \mathsf{ignite} \rceil \overset{0.5+\varepsilon}{\longrightarrow} \lceil \neg \mathsf{ignite} \rceil$ (Prog-2)  $\lceil \neg \mathsf{purge} \rceil$ ;  $\lceil \mathsf{purge} \rceil \stackrel{\leq 30}{\longrightarrow} \lceil \mathsf{purge} \rceil$ (Stab-2) 2

$\lceil \neg ignite \rceil$ ;  $\lceil ignite \rceil \stackrel{\leq 0.5}{\longrightarrow} \lceil ignite \rceil$

(Stab-3) (Syn-1)

$\lceil \mathsf{idle} \wedge H \rceil \overset{\varepsilon}{\longrightarrow} \lceil \neg \mathsf{idle} \rceil$

(Syn-2)

$\lceil \mathsf{burn} \wedge (\neg H \vee \neg F) \rceil \xrightarrow{\varepsilon} \lceil \neg \mathsf{burn} \rceil$  $\lceil \neg \mathsf{idle} \rceil$ ;  $\lceil \mathsf{idle} \land \neg H \rceil \longrightarrow \lceil \mathsf{idle} \rceil$

(Stab-1) (Stab-1-init)

$\lceil \mathsf{idle} \wedge \neg H \rceil \longrightarrow_0 \lceil \mathsf{idle} \rceil$  $\lceil \neg \mathsf{burn} \rceil$  ;  $\lceil \mathsf{burn} \land H \land F \rceil \longrightarrow \lceil \mathsf{burn} \rceil$

#### Controller: (local)

#### $\lceil \rceil \lor \lceil \mathsf{idle} \rceil$ ; true, (Init-1) $\lceil \mathsf{idle} \rceil \longrightarrow \lceil \mathsf{idle} \vee \mathsf{purge} \rceil$ (Seq-1) $[purge] \longrightarrow [purge \lor ignite]$ (Seq-2) $\lceil ignite \rceil \longrightarrow \lceil ignite \lor burn \rceil$ (Seq-3) $\lceil \mathsf{burn} \rceil \longrightarrow \lceil \mathsf{burn} \lor \mathsf{idle} \rceil$ (Seq-4) $\lceil \mathsf{purge} \rceil \overset{30+\varepsilon}{\longrightarrow} \lceil \neg \mathsf{purge} \rceil$ (Prog-1) $\lceil \mathsf{ignite} \rceil \overset{0.5+\varepsilon}{\longrightarrow} \lceil \neg \mathsf{ignite} \rceil$ (Prog-2) $\lceil \neg purge \rceil$ ; $\lceil purge \rceil \xrightarrow{\leq 30} \lceil purge \rceil$ (Stab-2) $\lceil \neg ignite \rceil$ ; $\lceil ignite \rceil \stackrel{\leq 0.5}{\longrightarrow} \lceil ignite \rceil$ (Stab-3) $\lceil \mathsf{idle} \wedge H \rceil \overset{\varepsilon}{\longrightarrow} \lceil \neg \mathsf{idle} \rceil$ (Syn-1) $\lceil \mathsf{burn} \wedge (\neg H \vee \neg F) \rceil \xrightarrow{\varepsilon} \lceil \neg \mathsf{burn} \rceil$ (Syn-2) $\lceil \neg \mathsf{idle} \rceil$ ; $\lceil \mathsf{idle} \land \neg H \rceil \longrightarrow \lceil \mathsf{idle} \rceil$ (Stab-1) $\lceil \mathsf{idle} \wedge \neg H \rceil \longrightarrow_0 \lceil \mathsf{idle} \rceil$ (Stab-1-init) $\lceil \neg \mathsf{burn} \rceil$ ; $\lceil \mathsf{burn} \land H \land F \rceil \longrightarrow \lceil \mathsf{burn} \rceil$ (Stab-4)

#### Gas Valve: (output)

#### Heating Request: (input)

$$\lceil \rceil \vee \lceil \neg H \rceil$$

;  $true$ , (Init-2)

#### Flame: (input)

4/42

# Implementable Gas Burner Controller: Correctness Proof

**Set** GB-Ctrl := Init-1  $\wedge \cdots \wedge$  Stab-7  $\wedge \varepsilon > 0$ .

In the following, we show

$$\models \mathsf{GB\text{-}Ctrl} \wedge A(\varepsilon) \implies \mathsf{Req\text{-}1}.$$

where  $A(\varepsilon)$  constrains the reaction time of computers executing the control program.

Read: if a program behaving like 'GB-Ctrl' is executed on a computer with reaction time  $\varepsilon$  such that  $A(\varepsilon)$  holds, then 'Req' is satisfied in the system.

#### Recall:

$$\operatorname{Reg} : \iff \Box (\ell \geq 60 \implies 20 \cdot \int L \leq \ell)$$

and (cf. Olderog and Dierks (2008))

$$\models \mathsf{Req}\text{-}1 \Longrightarrow \mathsf{Req}$$

for the simplified requirement

Req-1 :=

$$\Box(\ell \leq 30 \implies \int L \leq 1)$$

.

6/42

**Proof**: Let  $\mathcal{I}$  be an interpretation,  $\mathcal{V}$  a valuation, and [c,d] an interval with  $\mathcal{I},\mathcal{V},[c,d]\models\mathsf{GB-Ctrl}$ . Let  $[b, e] \subseteq [c, d]$ .

• Case 1:  $\mathcal{I}, \mathcal{V}, [b, e] \models [idle]$ From

we can conclude

$$\mathcal{I}, \mathcal{V}, [b, e] \models \Box(\lceil G \rceil \implies \ell \leq \varepsilon) \land \neg \Diamond(\lceil G \rceil; \lceil \neg G \rceil; \lceil G \rceil)$$

Thus  $\mathcal{I}, \mathcal{V}, [b, e] \models \int G \leq \varepsilon$ . by (Syn-3), the valve is closed within  $\varepsilon$  time units doesn't describe the synthetic of the synthetic o

closed within  $\varepsilon$  time units when in 'idle'

by (Stab-6), the valve doesn't open again when in 'idle'

• Case 2:  $\mathcal{I}, \mathcal{V}, [b, e] \models [purge]$  Analogously to case 1.

### Lemma 3.15 Cont'd

$$\begin{array}{c} \mathsf{GB\text{-}Ctrl} \implies \Box \left( \begin{array}{c} (\lceil \mathsf{idle} \rceil \Longrightarrow & \int G \leq \varepsilon) \\ \land (\lceil \mathsf{purge} \rceil \Longrightarrow & \int G \leq \varepsilon) \\ \land (\lceil \mathsf{ignite} \rceil \Longrightarrow \ell \leq 0.5 + \varepsilon) \\ \land (\lceil \mathsf{burn} \rceil \Longrightarrow \int \neg F \leq 2\varepsilon) \end{array} \right) \end{array}$$

• Case 3:  $\mathcal{I}, \mathcal{V}, [b, e] \models \lceil \text{ignite} \rceil$ From

$$[ignite] \xrightarrow{0.5+\varepsilon} [\neg ignite]$$

(Prog-2)

we can directly conclude  $\mathcal{I}, \mathcal{V}, [b, e] \models \ell \leq 0.5 + \varepsilon$ .

$\bullet \ \, \mathbf{Case} \ \, \mathbf{4} \hbox{:} \ \, \mathcal{I}, \mathcal{V}, [b,e] \models \lceil \mathsf{burn} \rceil \\ \mathsf{From} \ \,$

$\begin{array}{c|c} \hline | \lor [\neg F] \lor [F] \\ \lor [F]; [\neg F] \lor [\neg F]; [F] \\ \lor [\neg F] \\ \hline \end{array}$

we can conclude

$$\mathcal{I}, \mathcal{V}, [b, e] \models \underbrace{\Box \left( \lceil \neg F \rceil \implies \ell \leq \varepsilon \right)}_{\text{by (Syn-2)}} \land \underbrace{\neg \Diamond (\lceil F \rceil \, ; \lceil \neg F \rceil \, ; \lceil F \rceil)}_{\text{by (Stab-5)}}$$

Thus  $\mathcal{I}, \mathcal{V}, [b, e] \models \int \neg F \leq 2\varepsilon$ .

8/42

#### Lemma 3.16

$$\models \exists \, \varepsilon \bullet \mathsf{GB-Ctrl} \implies \underbrace{\Box (\ell \leq 30 \implies \int L \leq 1)}_{\mathsf{Req-1}}$$

**Proof**: Let  $\mathcal{I}$ ,  $\mathcal{V}$ , and [b, e] such that  $\mathcal{I}$ ,  $\mathcal{V}$ ,  $[b, e] \models \mathsf{GB-Ctrl} \land \ell \leq 30$ .

Distinguish 5 cases:

(i)

$$\mathcal{I}, \mathcal{V}, [b, e] \models \lceil \rceil$$

(ii)

$$\mathcal{I}, \mathcal{V}, [b, e] \models (\lceil \mathsf{idle} \rceil; true \land \ell \leq 30)$$

(iii)

$$\mathcal{I}, \mathcal{V}, [b, e] \models (\lceil \mathsf{purge} \rceil; true \land \ell \leq 30)$$

(iv)

$$\mathcal{I}, \mathcal{V}, [b, e] \models (\lceil \text{ignite} \rceil; true \land \ell \leq 30)$$

(v)

$$\mathcal{I}, \mathcal{V}, [b, e] \models (\lceil \mathsf{burn} \rceil; true \land \ell \leq 30)$$

### Lemma 3.16 Cont'd

• Case (i):  $\mathcal{I}, \mathcal{V}, [b, e] \models \lceil \rceil$

• Case (ii):  $\mathcal{I}, \mathcal{V}, [b,e] \models \lceil \mathsf{idle} \rceil$  ;  $true \land \ell \leq 30$

we can conclude

hence

By 3.15,

$$\mathcal{I}, \mathcal{V}, [b, e] \models \int L \leq 2\varepsilon$$

Thus  $\varepsilon \leq 0.5$  is sufficient for Req-1 (  $\int L \leq 1$  ) in this case.

10/42

### Lemma 3.16 Cont'd

$\bullet$  Case (iii):  $\mathcal{I}, \mathcal{V}, [b,e] \models \lceil \mathsf{burn} \rceil$  ;  $true \land \ell \leq 30$

From

$$\lceil burn \rceil \longrightarrow \lceil burn \lor idle \rceil$$

(Seq-4)

we can conclude

$$\begin{split} \mathcal{I}, \mathcal{V}, [b,e] &\models (\lceil \mathsf{burn} \rceil \lor \lceil \mathsf{burn} \rceil \, ; \underbrace{\lceil \mathsf{idle} \rceil \, ; \, true}) \land \ell \leq 30. \\ \mathsf{By 3.15 \ and \ Case (ii)}, & & & & & \\ \mathcal{I}, \mathcal{V}, [b,e] &\models (\int \!\!\!\!/ L \leq 2\varepsilon) \lor (\int \!\!\!\!/ L \leq 2\varepsilon) ; (\int \!\!\!\!/ L \leq 2\varepsilon) \land \ell \leq 30. \end{split}$$

hence

$$\mathcal{I}, \mathcal{V}, [b, e] \models \int L \leq 4\varepsilon.$$

Thus  $\varepsilon \leq 0.25$  is sufficient for Req-1 ( $\int L \leq 1$ ) in this case.

### Lemma 3.16 Cont'd

• Case (iv):  $\mathcal{I}, \mathcal{V}, [b,e] \models \lceil \text{ignite} \rceil$  ;  $true \land \ell \leq 30$  From

$$[ignite] \longrightarrow [ignite \lor burn]$$

(Seq-3)

we can conclude

$$\begin{split} \mathcal{I}, \mathcal{V}, [b,e] &\models (\lceil \mathsf{ignite} \rceil \vee \lceil \mathsf{ignite} \rceil; \underbrace{\lceil \mathsf{burn} \rceil; \mathit{true}}) \wedge \ell \leq 30. \\ \mathsf{By 3.15 \ and \ Case \ (iii)}, & & & \\ \mathcal{I}, \mathcal{V}, [b,e] &\models (\not [L \leq 0.5 + \varepsilon) \vee \not (f \ L \leq 0.5 + \varepsilon); \not (f \ L \leq 4\varepsilon) \wedge \ell \leq 30. \end{split}$$

hence

$$\mathcal{I}, \mathcal{V}, [b, e] \models \int L \leq 0.5 + 5\varepsilon.$$

Thus  $\varepsilon \leq 0.1$  is sufficient for Req-1 (  $\int L \leq 1$  ) in this case.

12/42

### Lemma 3.16 Cont'd

• Case (v):  $\mathcal{I}, \mathcal{V}, [b,e] \models \lceil \mathsf{purge} \rceil$  ;  $true \land \ell \leq 30$  From

$$[purge] \longrightarrow [purge \lor ignite]$$

(Seq-2)

and 3.15 and Case (iv) we can conclude

$$\mathcal{I}, \mathcal{V}, [b, e] \models \int L \leq 0.5 + 6\varepsilon.$$

Thus  $\varepsilon \leq \frac{1}{12}$  is sufficient for Req-1 ( $\int L \leq 1$ ) in this case.

Lemma 3.16.

$$\models \exists \varepsilon \bullet \mathsf{GB-Ctrl} \implies \underbrace{\Box(\ell \leq 30 \implies \int L \leq 1)}_{\mathsf{Req-1}}$$

- 9 - 2017-11-28 - Sgbiproof -

Theorem 3.17.

$$\models \left(\mathsf{GB-Ctrl} \wedge \varepsilon \leq \frac{1}{12}\right) \implies \mathsf{Req}$$

#### Recall:

- $\bullet \ \ \mathsf{Req\text{-}1} = \square(\ell \leq 30 \implies \smallint L \leq 1) \ \mathsf{implies} \ \mathsf{Req}.$

- $\bullet \ \ \textbf{3.15:} \ \lceil \mathsf{purge} \rceil \implies \smallint L \leq \varepsilon, \lceil \mathsf{ignite} \rceil \implies \smallint L \leq 0.5 + \varepsilon, \lceil \mathsf{burn} \rceil \implies \smallint L \leq 2\varepsilon, \lceil \mathsf{idle} \rceil \implies \smallint L \leq \varepsilon.$

| purge                               | ignite                                         | burn                       | idle                                | purge                    |

|-------------------------------------|------------------------------------------------|----------------------------|-------------------------------------|--------------------------|

| $-\ell \ge 30$ $\longrightarrow$    | $\longleftarrow \ell \geq 0.5 \longrightarrow$ |                            |                                     | ← ℓ ≥ 30 —               |

| $\widehat{\int L \leq \varepsilon}$ | $\widehat{\int L \le 0.5 + \varepsilon}$       | $\int L \leq 2\varepsilon$ | $\widehat{\int L \leq \varepsilon}$ | $\int L \le \varepsilon$ |

|                                     |                                                | $\int \leq 30$             |                                     |                          |

• Thus  $\int L \le 0.5 + 6 \varepsilon$ , so a sufficient reaction time constraint is  $A(\varepsilon) := \varepsilon \le \frac{1}{12}.$

14/42

### Discussion

• We used only

What about

$$\mathsf{Prog-1} = \lceil \mathsf{purge} \rceil \overset{30+\varepsilon}{\longrightarrow} \lceil \neg \mathsf{purge} \rceil$$

for instance?

### Discussion

We used only

What about

$$\mathsf{Prog-1} = \lceil \mathsf{purge} \rceil \overset{30+\varepsilon}{\longrightarrow} \lceil \neg \mathsf{purge} \rceil$$

for instance?

We only proved the **safety** property on leakage, we did not consider the (not formalised) **liveness** requirement: the controller **should do something** finally, e.g. heating requests should be served finally by trying an ignition.

15/42

### Content

- Correctness Proof for the Gas Burner Implementables

- Now where's the implementation?

- Programmable Logic Controllers (PLC)

- → How do they look like?

- What's special about them?

- ☐ The read/compute/write cycle of PLC

- Example: Stutter Filter

- Structured Text example

- Other IEC 61131-3 programming languages

- PLC Automata

- —(● Example: Stutter Filter

- → PLCA Semantics by example

- └- Cycle time

- 9 - 2017-11-28 - Scontent -

9 - 2017-11-28 - main

17/42

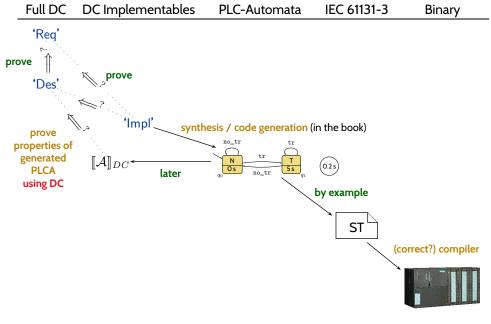

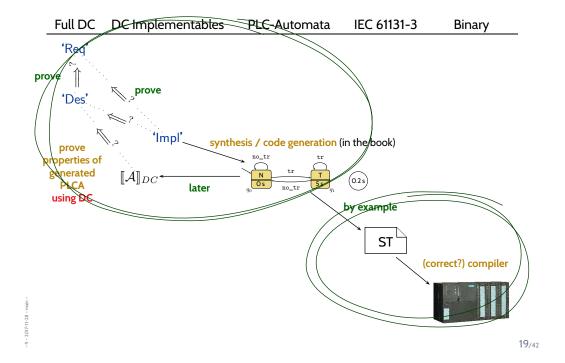

### The Plan

017-11-28 - main

18/42

#### Content

- Correctness Proof for the Gas Burner Implementables

- Now where's the implementation?

- Programmable Logic Controllers (PLC)

- → How do they look like?

- ─ What's special about them?

- The read/compute/write cycle of PLC

- Example: Stutter Filter

- —(● Structured Text example)

- Other IEC 61131-3 programming languages

- PLC Automata

- **Example**: Stutter Filter

- PLCA Semantics by example

- └- Cycle time

9 - 2017-11-28 - Scontent -

# What is a PLC?

21/42

# How do PLC look like?

- microprocessor, memory, timers

- digital (or analog) I/O ports

- possibly RS 232, fieldbuses, networking

- robust hardware

- reprogrammable

- standardised programming model (IEC 61131-3)

23/42

# Where are PLC employed?

- mostly process automatisation

- production lines

- packaging lines

- chemical plants

- power plants

- electric motors, pneumatic or hydraulic cylinders

- ..

- not so much: product automatisation, there

- tailored or OTS controller boards

- embedded controllers

- ...

-9-2017-11-28 - Solc -

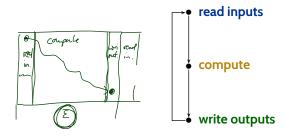

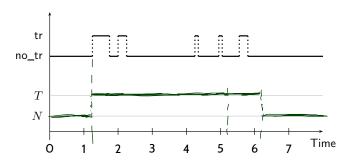

• PLC have in common that they operate in a cyclic manner:

- Cyclic operation is repeated until external interruption (such as shutdown or reset).

- Cycle time: typically a few milliseconds (Lukoschus, 2004).

- Programming for PLC means providing the "compute" part.

- Input/output values are available via designated local variables.

25/42

# How are PLC programmed, practically?

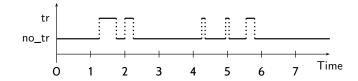

- Example: reliable, stutter-free train sensor.

- Assume a track-side sensor which outputs:

- no\_tr iff "no passing train"

- tr iff "a train is passing"

- Assume that a change from "no\_tr" to "tr" signals arrival of a train.

(No spurious sensor values.)

- Problem: the sensor may stutter,

i.e. oscillate between "no\_tr" and "tr" multiple times.

- 9 - 2017-11-28 - Splc -

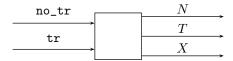

• Idea: a stutter filter with outputs N and T, for "no train" and "train passing" (and possibly X, for error).

After arrival of a train, it should ignore "no\_tr" for 5 seconds.

27/42

## How are PLC programmed, practically?

```

PROGRAM PLC_PRG_FILTER

2

state : INT := O; (* O:=N, 1:=T, 2:=X *)

3

tmr

ENDVAR

IF state = 0 THEN

%output := N;

8

%input = tr THEN

9

state := 1;

10

11

%output := T;

ELSIF %input = Error THEN

12

state := 2;

13

14

%output := X;

ENDIF

15

ELSIF state = 1 THEN

17

tmr(IN := TRUE, PT := t#5.0s);

18

IF (%input = no_tr AND NOT tmr.Q) THEN

19

20

state := 0;

%output := N;

21

tmr(IN := FALSE, PT := t#0.0s);

22

23

ELSIF %input = Error THEN

state := 2;

24

25

%output := X;

26

tmr( IN := FALSE, PT := t#0.0s );

ENDIF

27

ENDIF

```

compute write outputs

28/42

### How are PLC programmed, practically?

```

PROGRAM PLC_PRG_FILTER

VAR

2

3

state : INT := 0; (* 0:=N, 1:=T, 2:=X *)

: TP; —

4

tmr

ENDVAR

5

declare timer tmr

IF state = O THEN

%output := N;

IF %input = tr THEN

state := 1;

10

%output := T;

11

12

ELSIF %input = Error THEN

state := 2;

13

14

%output := X;

duration

15

ENDIF

ELSIF state = 1 THEN

16

17

tmr( IN := TRUE, PT := t#5.0s );

18

IF (%input = no_tr AND NOT tmr.Q) THEN

19

20

state := 0;

21

%output := N;

tmr( IN := FALSE, PT := t#0.0s );

22

ELSIF %input = Error THEN

23

state := 2;

24

%output := X;

25

tmr(IN := FALSE, PT := t#0.0s);

26

27

ENDIF

ENDIF

```

#### intuitive semantics:

- do the assignment

- if assignment changed IN from FALSE to TRUE ("rising edge on IN") then set tmr to given duration (initially, IN is FALSE)

TRUE: iff tmr is still running (here: if 5 s not yet elapsed)

28/42

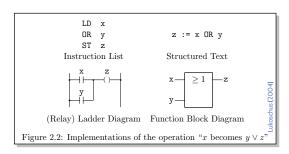

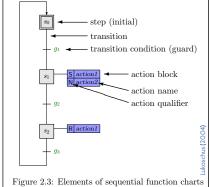

### Alternative Programming Languages by IEC 61131-3

Tied together by

Sequential Function Charts (SFC)

Unfortunate: deviations in semantics... Bauer (2003)

- 2017-11-28 - Solv

- Correctness Proof for the Gas Burner Implementables

- Now where's the implementation?

- Programmable Logic Controllers (PLC)

- → How do they look like?

- —(● What's special about them?

- The read/compute/write cycle of PLC

- Example: Stutter Filter

- Structured Text example

- Other IEC 61131-3 programming languages

- PLC Automata

- —(● Example: Stutter Filter

- PLCA Semantics by example

- □ Cycle time

39/42

#### Tell Them What You've Told Them...

- We can prove the Gas Burner implementables correct by carefully considering its phases.

- A crucial aspect is reaction time:

- Controller programs executed on some hardware platform do not react in 0-time,

- some platforms may be too slow to satisfy requirements.

- Programmable Logic Controllers (PLC) are epitomic for real-time controller platforms:

- have a real-time clock device,

- · can read inputs and write outputs,

- can manage local state.

- PLC programs

- are executed in read/compute/write cycles,

- have a cycle-time (possibly a watchdog).

- PLC Automata are a more abstract (than IEC 61131-3) way of describing and studying PLC programs.

9 - 2017-11-28 - Sttwytt -

# References

- 9 - 2017-11-28 - main -

41/42

# References

Bauer, N. (2003). Formale Analyse von Sequential Function Charts. PhD thesis, Universität Dortmund.

Lukoschus, B. (2004). *Compositional Verification of Industrial Control Systems*. PhD thesis, Christian-Albrechts-Universität zu Kiel.

Olderog, E.-R. and Dierks, H. (2008). *Real-Time Systems - Formal Specification and Automatic Verification*. Cambridge University Press.

9 - 2017-11-28 - main -