## Zusammenfassung

Graphische Spezifikation von Kommunikationsabläufen mittels Szenarien erfreut sich großer Beliebtheit, vor allem wegen ihrer Einfachheit und Intuitivität. Die beiden in diesem Bereich existierenden Standards, Message Sequence Charts (MSC) und Sequence Diagrams (SD), schöpfen aufgrund von mangelnder Ausdruckskraft und fehlender semantischer Fundierung ihre Möglichkeiten im Hinblick auf den erzielbaren Nutzen nicht voll aus. Zudem sind sowohl MSCs als auch SDs in erster Linie auf den Einsatz in einem informellen, exemplarischen Kontext ausgerichtet. Ziel dieser Arbeit ist es, die Grundlage für einen weitergehenden Einsatz von Sequence Charts, insbesondere in der formalen Verifikation, zu schaffen. Ein Ansatz in diese Richtung sind die von Damm und Harel vorgestellten Live Sequence Charts (LSC).

Kernpunkt von LSCs ist die Unterscheidung zwischen möglichem und geforderten Verhalten. Auf oberster Ebene erlaubt dies die Spezifikation von einzuhaltenden Abläufen, zusätzlich zu exemplarischen Abläufen in MSCs und SDs. Weiterhin ist es in LSCs möglich Lebendigkeitseigenschaften zu formulieren, wie etwa das Ankommen einer Nachricht. Andere wichtige Neuerungen sind die Aufwertung von Bedingungen zu booleschen Ausdrücken, sowie die Möglichkeit, den Aktivierungszeitpunkt einer Chart mittels einer Bedingung zu charakterisieren.

Der von Damm und Harel vorgeschlagene Sprachumfang wird im Rahmen dieser Arbeit um weitere essentielle Konstrukte ergänzt, wie Zeitbedingungen, Gleichzeitigkeit von Ereignissen, sowie die Möglichkeit, die Aktivierung einer Chart durch Nachrichtensequenzen auszulösen. Des weiteren wird die Spezifikation von Annahmen über das Umgebungsverhalten innerhalb der LSC, die das gewünschte Systemverhalten ausdrückt, ermöglicht.

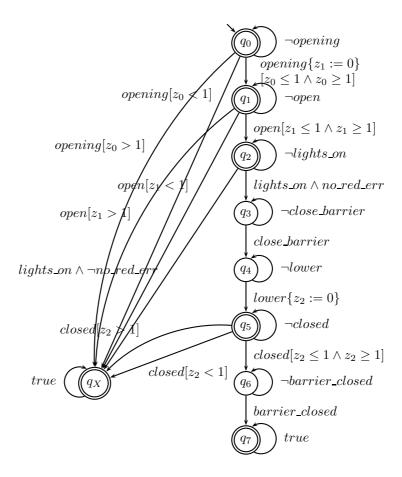

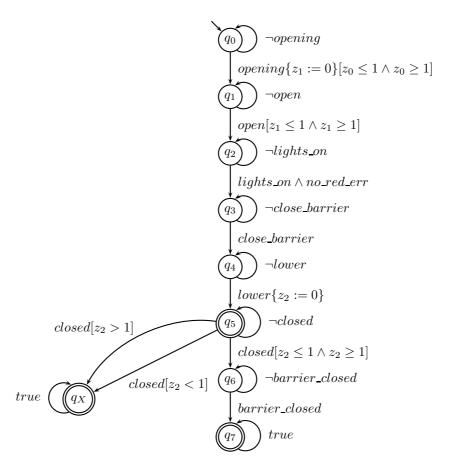

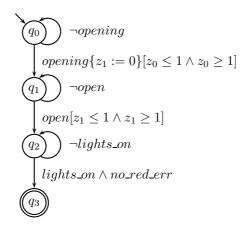

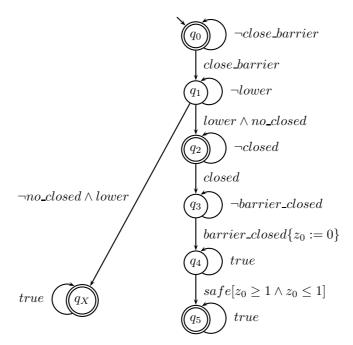

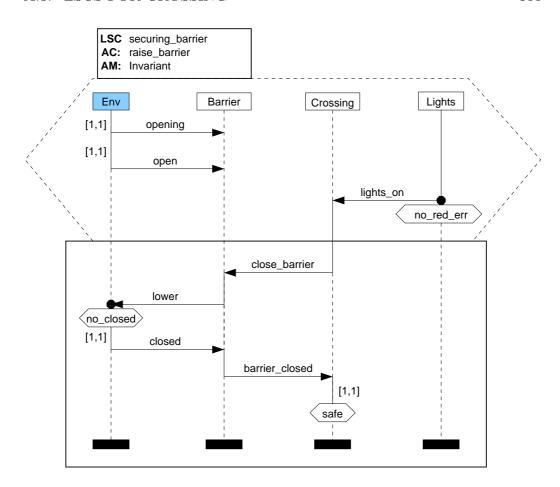

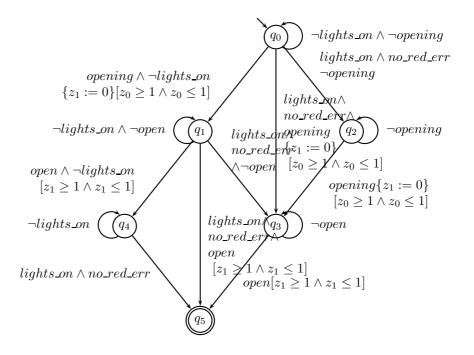

Neben der Festlegung des LSC-Sprachumfangs ist die Definition der formalen Semantik von LSCs zentraler Punkt dieser Dissertation. Die Semantik wird konstruktiv definiert durch Abbildung einer LSC in einen endliche Automaten (zeitbehaftete Büchi-Automaten), unter Berücksichtigung der in der LSC ausgedrückten partiellen Ordnung zwischen den einzelnen LSC Elementen.

Das Sprachdesign wird abgerundet durch eine Einordnung von LSCs in einen modellbasierten Entwicklungsprozeß, wobei das Ziel ist, Wissen in Form von einmal spezifizierten LSCs soweit möglich in späteren Phasen des Entwurfs wiederzuverwenden. Abschließend erfolgt eine Untersuchung der praktischen Anwendbarkeit der entwickelten Spezifikationssprache am Beispiel der formalen Verifikation von STATEMATE-Modellen. Hierbei werden die zu überprüfenden Anforderungen als LSCs spezifiziert.

## Abstract

Graphical description of message exchange by means of scenarios is a popular specification technique, especially due to the intuiveness provided. The prevalent standards in this area, Message Sequence Charts (MSC) und Sequence Diagrams (SD), are lacking both expressiveness and formal foundation. Additionally, they are used almost exclusively in an exemplary fashion describing typical system interactions. The goal of this thesis is the creation of a sound basis for the application of sequence charts to other, more advanced use cases like formal verification. An approach along this line of thought has been presented by Damm and Harel in the form of Live Sequence Charts (LSC).

The basic idea of LSCs is the distinction between possible and mandatory elements allowing, at the level of an entire chart, the specification of required behavior in addition to the sample interactions of MSCs and SDs. At a more fine-grained level this feature creates the possibility to express liveness properties like the mandatory receipt of a message. Other novel features are the upgrade of conditions to boolean expressions and the characterization—via an activation condition—of when the chart is to be activated.

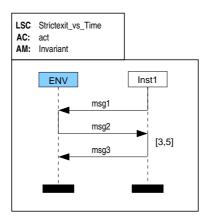

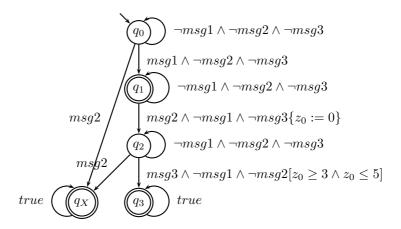

This thesis extends the LSC language as proposed by Damm and Harel by several missing, but essential features like time constraints, simultaneity of events as well as activation of an LSC by a sequence of interactions. Another important new feature is the possibility to specify assumptions about environment behavior directly within the LSC describing the desired system behavior.

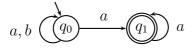

The definition of the formal semantics of LSCs is the second major part of this thesis. The semantics is defined in a constructive fashion by transforming an LSC into a timed Büchi automaton capturing the partial order prescribed by the LSC elements.

The language design is completed by a presenting a methodology which embeds LSCs into a model-based development process. The goal is to reuse knowledge about the system, recorded in the form of LSCs, in later phases of development. The rear of this thesis is brought up by an evaluation of the applicability of the developed specification language. The formal verification of Statemate models is chosen as a sample field of application, where the properties to be verified are specified by LSCs.

# Acknowledgments

A major piece of work, like this thesis, is seldom created in isolation. At this point I therefore would like to gratefully acknowledge those people, which have helped me to achieve this success.

First of all I would like to thank Werner Damm, who provided me with the opportunity to write this thesis. I have greatly benefitted from his encouragement and the creative working environment he created. His knowledge and support have been an invaluable resource during the last five years. I furthermore thank Ernst-Rüdiger Olderog, who was kind enough to act as the second reviewer for my thesis. Additional thanks go to David Harel for the vivid discussions on issues of design and semantics of the LSC language.

Another key ingredient for the existence of this thesis is the working group in which I have been working in Oldenburg. I have had many interesting and helpful discussions with the people in this working group and have profited from their expertise and experience. I especially thank Hartmut Wittke, with whom I have shared many thoughts and ideas on the subjects of this thesis. He also contributed to a substantial degree in the integration of the LSC tools into the existing Statemate verification environment, thus helping to make the verification of LSCs become a reality. He was the most assidious proof readers, as well. I furthermore thank Tom Bienmüller and Alexander Metzner. They not only have contributed to this thesis by discussing semantical details, proof reading and general comments, but also shared an office with me. The congenial atmosphere of this "center of knowledge" was extremely motivating and enjoyable. Further thanks go to Martin Fränzle, who gave valuable comments on the automata-theoretic part, and Hans Jürgen Holberg, who provided me with feedback regarding the methodology and application of LSCs. I also thank Olaf Bär, Uwe Higgen and Rainer Koopmann, who carried out the initial implementation of the tools supporting the formal verifiction of LSCs. Moreover, I thank Andreas Thums for his collaboration on the Statemate case study.

Last, but certainly not least, I thank my parents for their support, not only in this endeavor. They have always encouraged me in what I was doing, for which I am deeply grateful.

# Contents

| 1 | Inti | roduct  | ion                                        | 1  |

|---|------|---------|--------------------------------------------|----|

| 2 | San  | nple A  | pplication: A Radio-based Signaling System | 23 |

|   | 2.1  | Gener   | ral Description                            | 23 |

|   | 2.2  |         | EMATE Model                                |    |

|   |      | 2.2.1   | Activity Chart SYSTEM                      |    |

|   |      | 2.2.2   | Activity Chart TRAIN                       |    |

|   |      | 2.2.3   | Activity Chart COMMUNICATION               | 36 |

|   |      | 2.2.4   | Activity Chart CROSSING                    |    |

| 3 | Mes  | ssage S | Sequence Charts and Sequence Diagrams      | 45 |

|   | 3.1  |         | ge Sequence Charts                         | 45 |

|   |      |         | MSC-93                                     |    |

|   |      | 3.1.2   |                                            |    |

|   |      | 3.1.3   | MSC-2000                                   |    |

|   |      | 3.1.4   |                                            |    |

|   | 3.2  | Seque   | nce Diagrams                               |    |

| 4 | Live | e Sequ  | ence Charts: The Kernel Language           | 65 |

|   | 4.1  | _       | LSC Features                               | 66 |

|   |      | 4.1.1   | Instances and Messages                     |    |

|   |      | 4.1.2   |                                            |    |

|   |      | 4.1.3   | Local Invariants                           |    |

|   |      | 4.1.4   |                                            |    |

|   | 4.2  | Activa  | ation and Quantification                   |    |

| 5 | Aut  | tomata  | a-Theoretic Foundation                     | 81 |

| - |      |         | -Automata                                  | 82 |

vi *CONTENTS*

|   | 5.2  | Timed Büchi Automata                                   | 4 |

|---|------|--------------------------------------------------------|---|

|   | 5.3  | Symbolic Automata                                      | 7 |

| 6 | Sen  | nantics of the LSC Kernel Language 93                  | 3 |

|   | 6.1  | Formal Syntax                                          | 4 |

|   | 6.2  | Formal Semantics                                       |   |

|   |      | 6.2.1 Basic Automaton Construction                     | 3 |

|   |      | 6.2.2 Self Loop Annotation                             | 4 |

|   |      | 6.2.3 Location Temperatures                            |   |

|   |      | 6.2.4 Semantics of Conditions                          | 3 |

|   |      | 6.2.5 Message Temperatures                             | 3 |

|   |      | 6.2.6 Local Invariants                                 | 3 |

|   |      | 6.2.7 The Unwinding Algorithm                          | 1 |

|   | 6.3  | Activation and Quantification                          | 1 |

|   |      | 6.3.1 Reference System                                 | 1 |

|   |      | 6.3.2 Complete Semantics                               | 4 |

|   |      | 6.3.3 Implications on the Interpretation               | 6 |

|   |      | 6.3.4 Well-formedness Rules                            | 3 |

|   | 6.4  | Related Work                                           | 9 |

| 7 | Ado  | ding Time 155                                          | 3 |

| • | 7.1  | Time Constraints in LSCs                               |   |

|   | 7.2  | Formal Semantics                                       |   |

|   |      | 7.2.1 Formal Syntax                                    |   |

|   |      | 7.2.2 The Timed Unwinding Algorithm 159                |   |

|   | 7.3  | Related Work                                           |   |

| 8 | Into | egrated Assumption Treatment 173                       | 1 |

| O | 8.1  | Internal Assumptions                                   |   |

|   | 0.1  | 8.1.1 Adjustment of the Formal Semantics               |   |

|   |      | 8.1.2 Unwinding Algorithm for Internal Assumptions 17' |   |

|   | 8.2  | External Assumptions                                   |   |

|   | 0.2  | 8.2.1 Extracting Assumptions from LSCs                 |   |

|   |      | 8.2.2 User Specified Assumptions                       |   |

|   | 8.3  | Semantics of External Assumptions                      |   |

|   | 8.4  | Related Work                                           |   |

|   |      |                                                        |   |

| CONTENTS | vii |

|----------|-----|

|          |     |

| 9            |       | grading Activation: Pre-charts                         | 205   |

|--------------|-------|--------------------------------------------------------|-------|

|              | 9.1   | Pre-charts                                             |       |

|              | 9.2   | Formal Semantics                                       |       |

|              |       | 9.2.1 Pre-chart Unwinding Algorithm                    |       |

|              | 9.3   | 9.2.2 Pre-charts Semantics                             |       |

|              | 9.5   | Related Work                                           | . 210 |

| 10           | Eml   | pedding LSCs into the Development Process              | 221   |

|              |       | Abstract Development Process                           |       |

|              | 10.2  | Advanced Use Cases for LSCs                            | . 223 |

|              |       | 10.2.1 Capturing Typical System Interactions           | . 223 |

|              |       | 10.2.2 Debugging by Existential Verification           |       |

|              |       | 10.2.3 From Scenarios to Protocol Specifications       |       |

|              |       | 10.2.4 Test Vector Generation                          | . 235 |

|              | 10.3  | Related Work                                           | . 236 |

| 11           | A 554 | essment of the LSC Language                            | 239   |

|              |       | Property Specification for Statemate                   |       |

|              |       | 11.1.1 Integration of LSCs into the STVE               |       |

|              |       | 11.1.2 Property Specification for Synchronous Models   |       |

|              |       | 11.1.3 Property Specification for Asynchronous Models  |       |

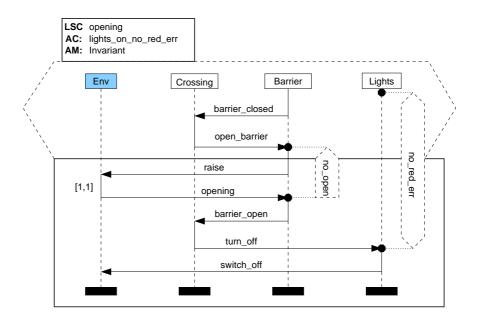

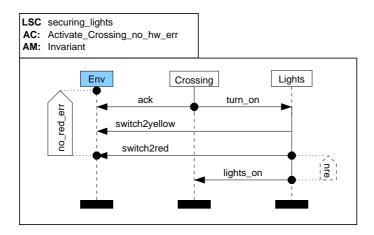

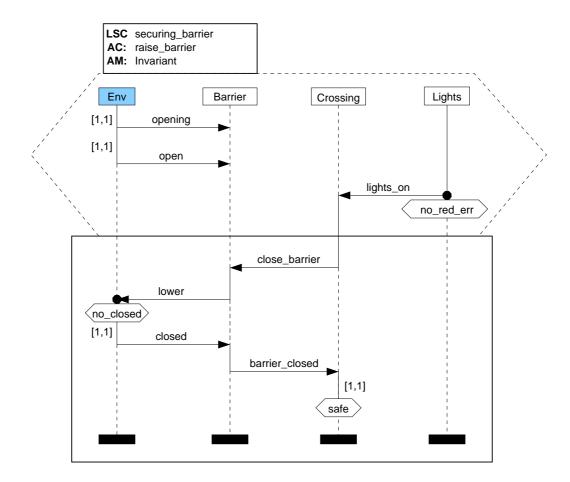

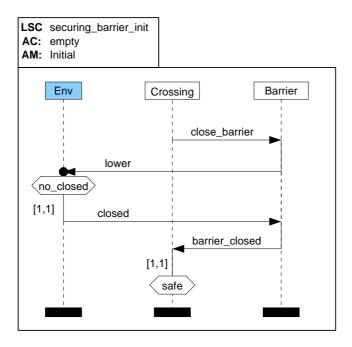

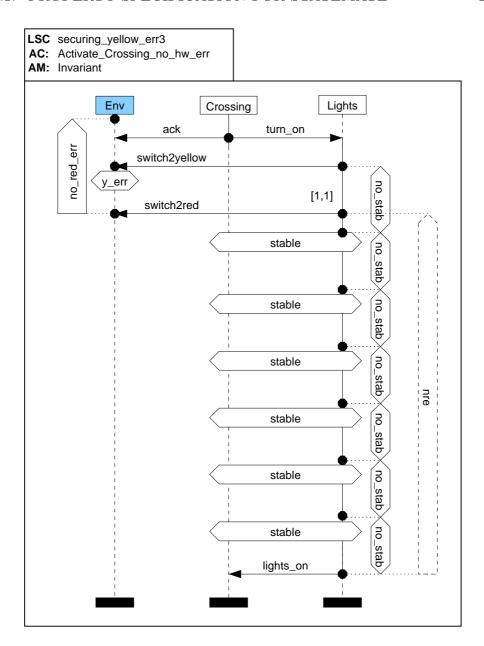

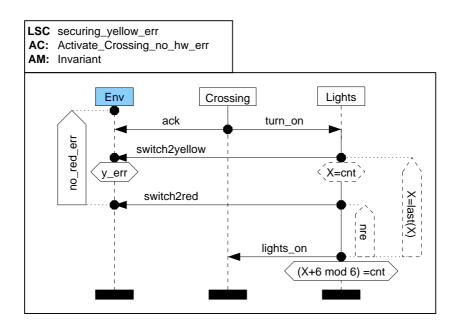

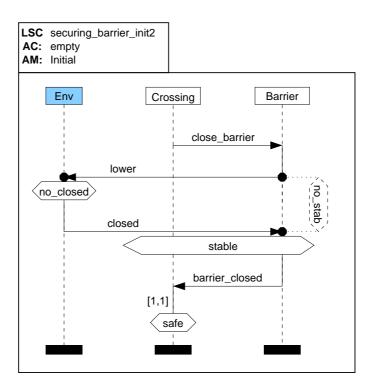

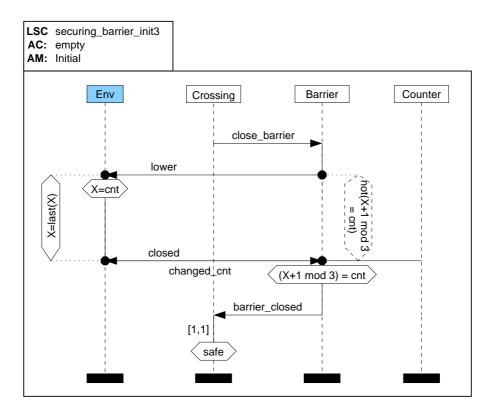

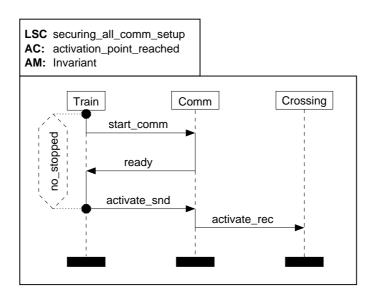

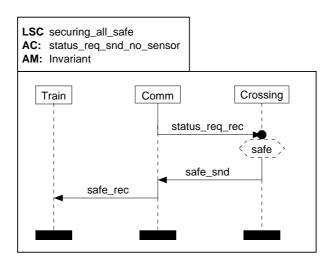

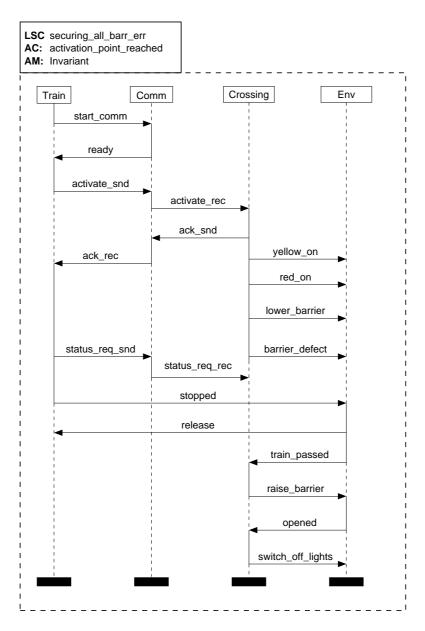

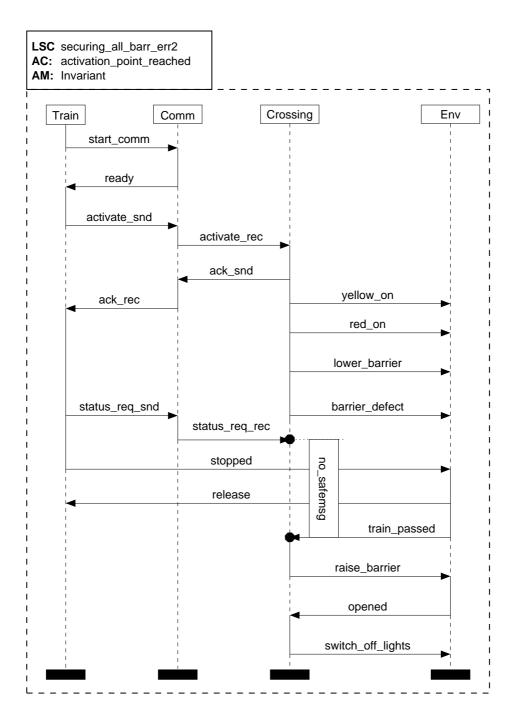

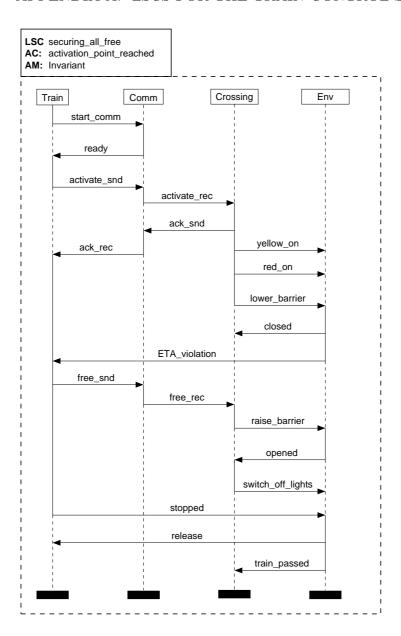

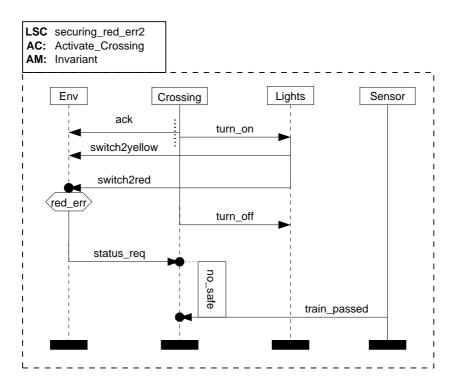

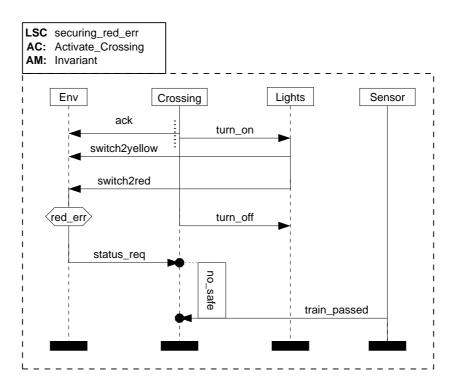

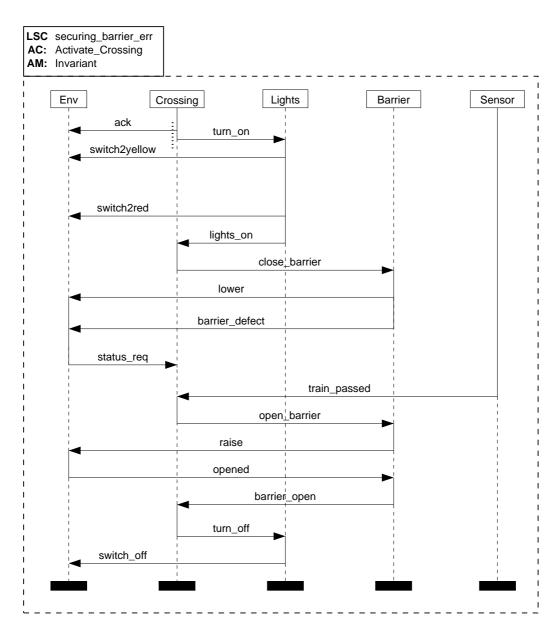

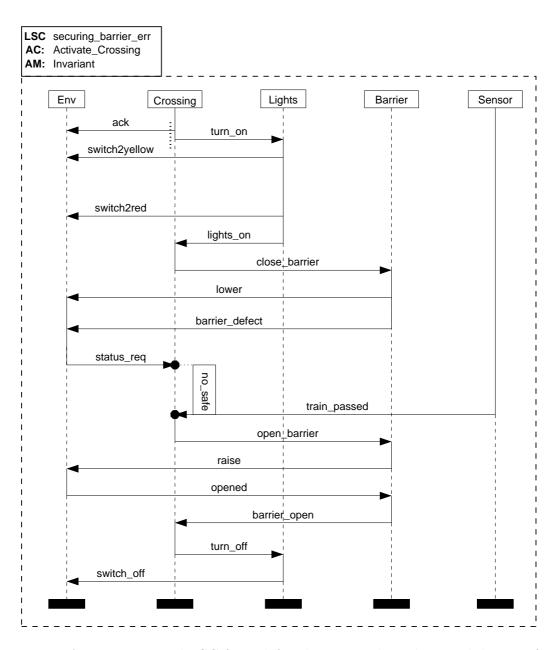

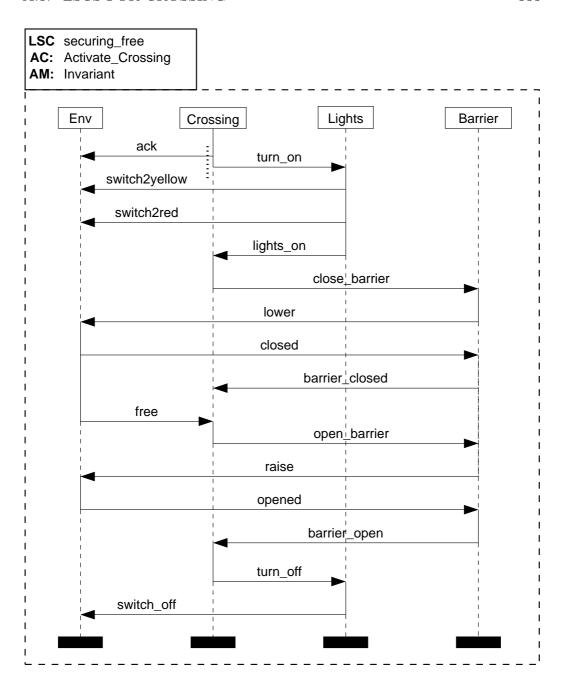

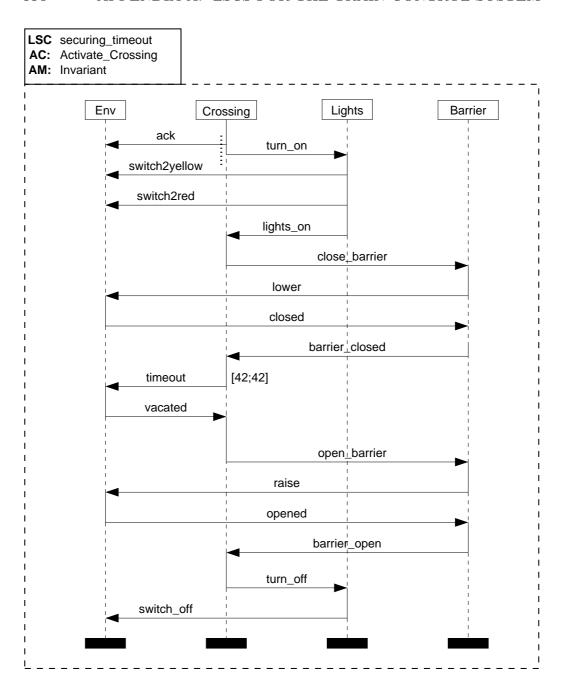

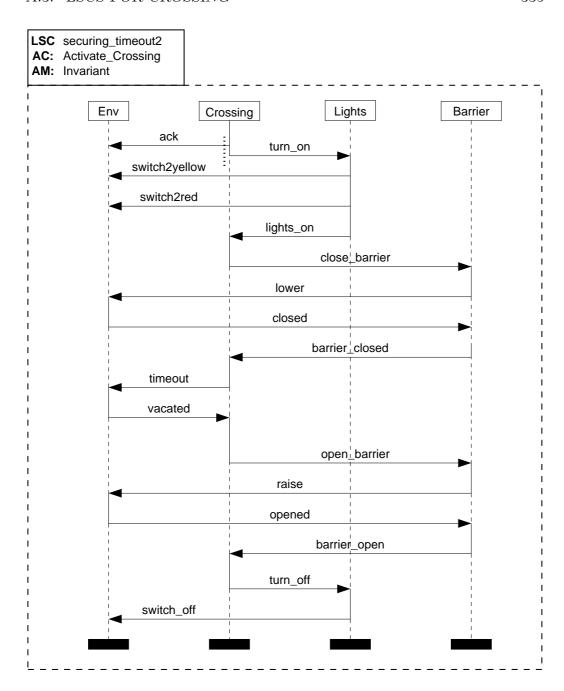

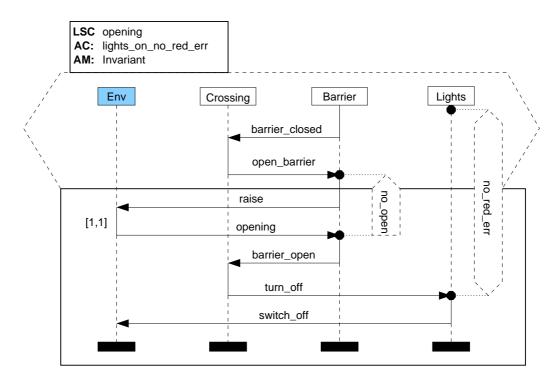

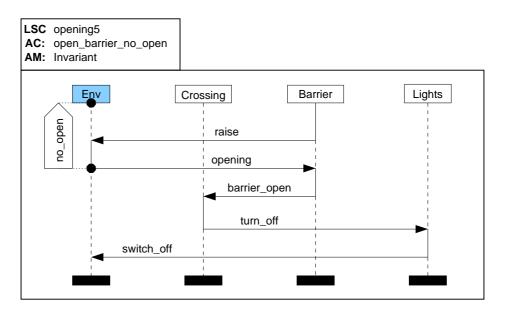

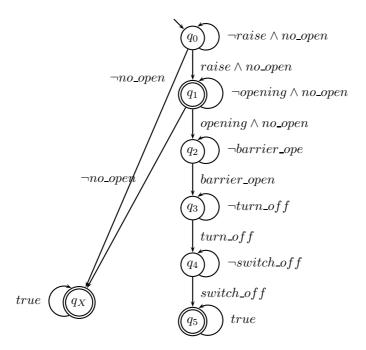

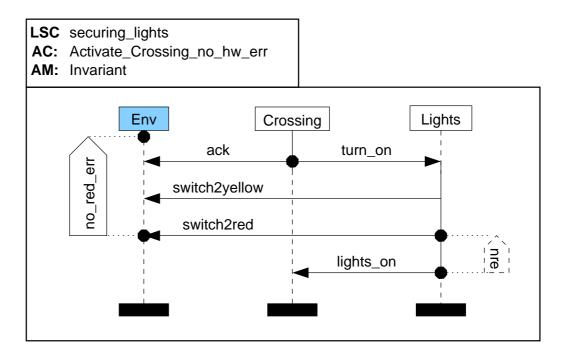

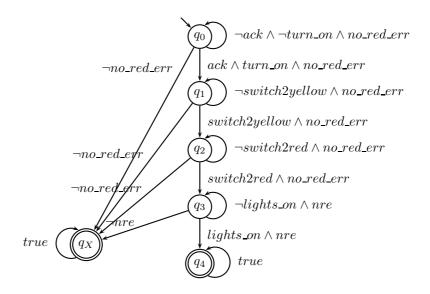

|              | 11.2  | Specification of the LSCs for the Train Control System |       |

|              |       | Verification Results                                   |       |

|              |       | 11.3.1 General Considerations                          | . 263 |

|              |       | 11.3.2 Existential Verification Results                |       |

|              |       | 11.3.3 Universal Verification Results                  | . 273 |

|              | 11.4  | Assessment of LSCs                                     |       |

| 12           | Con   | clusion and Outlook                                    | 291   |

| $\mathbf{A}$ | LSC   | s for the Radio-based Train Control System             | 297   |

|              | A.1   | LSCs for System                                        | . 298 |

|              |       | A.1.1 Existential LSCs                                 |       |

|              |       | A.1.2 Universal LSCs                                   |       |

|              |       | A.1.3 Assumption LSCs                                  | . 318 |

|              | A.2   | LSCs for Train                                         | . 320 |

|              |       | A.2.1 Existential LSCs                                 | . 320 |

|              |       | A.2.2 Universal LSCs                                   | . 323 |

| viii | ( | CONTENTS |

|------|---|----------|

|      |   |          |

|   | A.3            | LSCs t  | for C              | rossii   | ng.     |              |                        |          |          |        |   |   |             |   |    |     |    |    |     |            |          |    | . 3        | 25       |

|---|----------------|---------|--------------------|----------|---------|--------------|------------------------|----------|----------|--------|---|---|-------------|---|----|-----|----|----|-----|------------|----------|----|------------|----------|

|   |                | A.3.1   | Exis               | stenti   | al I    | LS(          | $\mathbb{C}\mathbf{s}$ |          |          |        |   |   |             |   |    |     |    |    |     |            |          |    | . 3        | 25       |

|   |                | A.3.2   | Uni                | versa    | l LS    | SCs          | s .                    |          |          |        |   |   |             |   |    |     |    |    |     |            |          |    | . 3        | 36       |

|   |                | A.3.3   | Ass                | umpt     | ion     | LS           | SCs                    |          |          |        |   |   |             |   |    |     |    |    |     |            |          |    | . 3        | 74       |

| _ | тс             | . •     | _                  |          |         |              | ~                      |          | <b>.</b> |        | _ | c | <b>41</b> . |   | a, | _ 1 |    |    |     |            | <b>.</b> | 1  | ۵1         |          |

| В |                | rmatic  |                    |          |         |              |                        |          |          |        | C | Ι | τn          | е | St | at  | en | 1a | ιτe | <b>)</b> [ | VI       | oa |            | 21       |

| В | for            | the Tra | ain (              | Cont     | rol     | $\mathbf{A}$ | $\mathbf{p}\mathbf{p}$ | lica     | tio      | on     |   |   |             |   |    |     |    |    |     |            |          |    | 38         | 81<br>21 |

| В | for<br>B.1     |         | ain (              | Cont     | rol     | <b>A</b>     | <b>pp</b> ]            | lica<br> | tio      | on<br> |   |   |             |   |    |     |    | •  |     |            |          |    | <b>3</b> 8 | 81       |

| В | for B.1<br>B.2 | the Tra | ain (<br>ants<br>M | Cont<br> | rol<br> | <b>A</b>     | pp<br><br>             | lica<br> | tio      | on<br> |   |   |             |   |    |     |    |    |     |            |          |    | 38<br>. 38 | 81<br>81 |

# Chapter 1

# Introduction

The amount of modern products containing hard and software components is becoming larger and larger. The type of products containing computer technology ranges from coffee and washing machines to cars and trains. These computer systems are embedded into a physical environment, which provides input data to these *embedded controllers* and which is in turn affected by the embedded controller. An airbag controller for instance reads sensor data, which indicate if a crash has occurred, and activates the firing capsule in this case. A train control system, as another example, uses various sensors to determine the position and velocity of a train, computes the maximum speed for the current position and checks, if the train is going too fast.

Not only does the number of products containing embedded controllers increase, but also the number of embedded controllers within a single product: a modern high-end car e.g. may contain up to seventy embedded controllers. This proliferation of embedded controllers is accompanied by a rising demand for more functionality entailing more complex embedded controllers. Following the general trend there is also a rising number of embedded controllers performing safety-critical tasks. The incorrect computation or supervision of a train's speed e.g. may lead to a derailed train involving severe damage to people and material.

The development of embedded controllers today typically starts with a requirement specification document written in natural language. Such informal specifications have the inherent danger of being ambiguous, inconsistent and incomplete — especially since such documents can consist of several hundred pages — and lead to errors and incompatibilities, which often are detected only later in the design process. The later an error is found, the more costly — both in terms of money and time — it is to remove, since

each step back in the development cycle means that the following steps have to be re-taken as well. In order to reduce the overall development costs it is thus imperative to uncover errors as early as possible.

Validation that the embedded controller conforms to the requirements specified initially is carried out by *testing*, i.e. by applying inputs to the controller and observing, if the correct outputs are produced. The testing process today is mostly carried out manually by test engineers, which rely on their experience and intuition for finding good test cases covering the relevant parts of the design. Clearly, the informal and often inconsistent process of embedded controller development today is not an optimal base for producing correct controllers in the most economic fashion, especially when considering safety-critical applications and the increasing complexity of the tasks, which are to be performed by the embedded controllers.

In order to guarantee the correctness and reliability of safety-critical electronic control units one prominent proposition is the adoption of an appropriate development process. Such a process structures the development into different phases, defines the activities to be performed in the phase, which documents are to be produced, etc. Examples for development processes are the V-model [ESt97], which has been defined for developing software for the German armed forces, and the CENELEC¹ norm EN 50128 [CEN01], which regulates the development of software for railway applications.

One approach, which addresses the abovementioned deficiencies of ambiguity and inconsistency, is known as *model-based development process*. The central idea is to construct an abstract model of the embedded controller capturing the requirements of the initial textual specification. Depending on the concrete needs and focus of the developed embedded controller different aspects — like e.g. functionality and decomposed structure — are reflected in the model. Modern CASE-tools<sup>2</sup> like e.g. STATEMATE [HLN<sup>+</sup>90] or various UML<sup>3</sup> tools [OMG01] provide support for such a development process and also offer graphical representations for the modeling of the embedded controller.

The abstract models allow the user to formalize the textual requirements and thus to more easily detect inconsistencies, ambiguities and incomplete specifications. Several tools, e.g. Statemate, additionally offer simulation

<sup>&</sup>lt;sup>1</sup>Comité Européen de Normalisation Electrotechnique

<sup>&</sup>lt;sup>2</sup>Computer Aided Software Engineering

<sup>&</sup>lt;sup>3</sup>Unified Modeling Language

capabilities allowing to directly observe and influence the dynamical behavior of the model. This feature is referred to as executable specification and enables the user to gain a good understanding of how the embedded controller behaves dynamically. Moreover, it allows to change or add features and assess their impact without much effort or risk. If the embedded controller comprises several (logical or physical) components, it is possible to examine their combined dynamic behavior before a concrete implementation is available yielding a virtual integration. A model-based development hence allows to assess the functionality of the designed embedded controller at a very early stage in the design process removing ambiguities and inconsistencies, which would otherwise have potentially led to errors discovered only in later phases. The abstract representation constructed serves as a reference model (also called *golden device*) for the later stages of the development. Possible applications in this direction are for instance the automatic generation of code from the reference model and deriving test vectors for unit or integration testing.

### Formal Verification

The model-based development process tackles the problem of ambiguous and inconsistent requirement specifications. The correctness of the designed embedded controller wrt. to its requirements is another vital property, which has to be guaranteed especially for safety-critical applications. In view of the increasing embedded controller complexity it is clear that the traditional testing approach is not sufficient to ensure correctness under *all* circumstances. The number of possible combinations of input stimuli and possible sequences thereof is too large to be tested in its entirety for industrial-sized embedded controllers. Testing thus considers only a finite set of test cases chosen by the test engineers.

In recent years formal verification has been developed in order to guarantee correctness under all circumstances. Formal verification entails a formal mathematical proof that a model satisfies the specified requirements. In combination with the model-based development process formal verification demonstrates the correctness of the model wrt. the specified requirements lending more weight to the reference model. In this way the requirement that "a train never passes a not secured crossing" can be proven for all possibilities of sequences of input stimuli.

Within the field of formal verification, there are three major approaches: theorem proving, model checking and bounded model checking. The basic idea of theorem proving is to support the user in constructing a proof calculus, which demonstrates the validity of the specified requirement. Theorem provers, like e.g. the popular PVS [OS97], require a large amount of user interaction and expert knowledge, since they provide computer-based support for the formal reasoning, which has to be carried out by the user.

Model checking is a fully automatic technique, which has been invented independently by two research groups (Clarke and Emerson [CE81] on the one hand and Quielle and Sifakis [QS82] on the other). Today's model checkers use a symbolic representation (see [BCM<sup>+</sup>92, McM93]) of the model for greater efficiency, so that this technique is called *symbolic model checking*. In the remainder we use the term 'model checking' instead of symbolic model checking for simplicity's sake.

A model checker requires two inputs: the model to be examined and the requirement to be proven. The former input is given as a *Finite State Machine* (FSM), which formally describes the behavior of the model. The requirement is stated in *temporal logic* [Eme90, MP92], which adds temporal operators to the standard boolean operators ' $\land$ ', ' $\lor$ ' and ' $\lnot$ '.

The model check algorithm determines, if the model satisfies the specified property under all circumstances, i.e. all possible sequences of input combinations are examined. The result is either 'true', if there is no way to violate the property, or 'false' otherwise. In the latter case the model checker produces a counter example, also called error path or witness, showing the sequence of input stimuli, which lead to the violation of the requirement. The counter example can be examined by the verifier and thereby gives valuable insight to the cause why the property does not hold. This feature is another reason why model checking has become more and more popular in recent years. The details of the symbolic model checking are not relevant in this work and can be found in [BCM<sup>+</sup>92], [McM93] or [CGP99].

The strategy of bounded model checking [BCCZ99] is to examine the model up to a depth k starting from the initial state and check, if the property is violated in this part of the model. If a violation is detected, a counter example is returned. If no violation is found, the result is inconclusive, since a violation might exist at a depth greater than k. The bound k is hence increased and the property is checked again. The actual checking procedure for each incomplete model FSM of depth k is formulated as a task for so-called SAT-checkers, which have been developed to efficiently solve propositional

satisfiability problems [DP60].

The crucial point is to know when to stop increasing the bound, i.e. when an increased depth does not add new states, which have not been examined before. This maximal bound is called diameter and depends on both the model and the property to be checked. The diameter of a given proof can be computed, but in practice this is efficiently possible only for small models, so that in practical applications k is provided by the user or given a default value. Thus, the part of bounded model checking, which is applied in practice, is an incomplete method.

# Simplified Property Specification

Temporal logic formulas expressing real world requirements can quickly become fairly complex and hard to understand. Correct specification of non-trivial properties in terms of temporal logic requires considerable expert knowledge. Several approaches exist, which try to provide other, simpler means to specify properties. This is one step in order to enable non-expert users to employ formal verification techniques in practice, the other step being an easy and preferably automatic way to construct an FSM. This section presents the approaches dealing with the property side.

Two fundamental ideas are distinguished: one restricting the user to chose a specification pattern or template from a set of often recurring patterns and instantiate its parameters with the concrete model elements in order to specify the desired requirement. This method bases on the observation that often requirements are identical, except for the concrete variables used. The analysis of typical requirements thus leads to the identification of recurring patterns, which are offered as templates for requirement specification. For each such pattern the formal basis, e.g. temporal logic, is defined once and the user only chooses an appropriate pattern without having to wrestle with the low-level particulars. Examples for different pattern libraries are the ones compiled by Dwyer et al. [DAC98, DAC99], which allow patterns to be instantiated for a number of formalisms, e.g. LTL (linear time temporal logic) and CTL (computation tree logic) formula or Quantified Regular Expressions, and the one by Bitsch [Bit00, Bit01]. The STATEMATE Verification Environment (see below) also offers a library of specification patterns [OSC02a].

A variant of the pattern-based approach is the use of a restricted subset of natural language, which can be transformed into a temporal logic formula. Holt and Klein [HK99, Hol99] e.g. use a subset of the English language in order to specify CTL formulas and Ruf et al. [FMR00] combine the structured natural language approach with specification patterns by allowing the user to construct sentences from preselected natural language fragments and instantiating parameters.

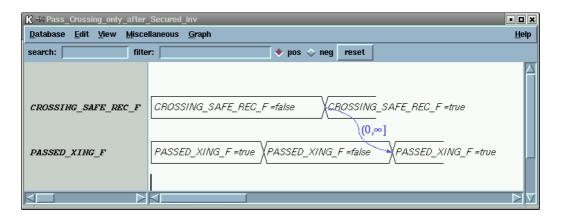

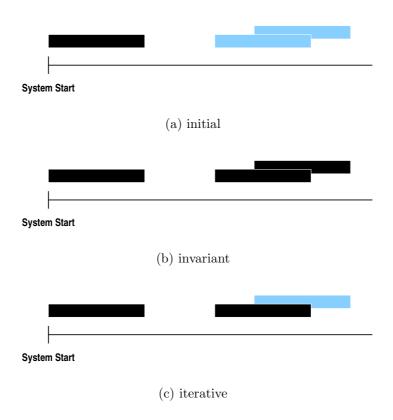

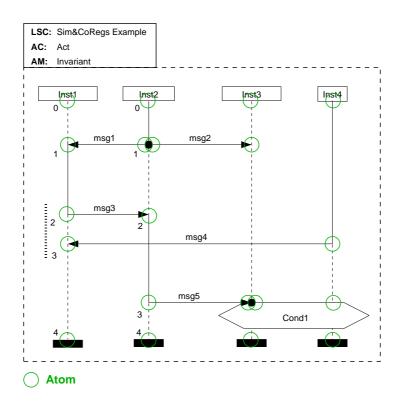

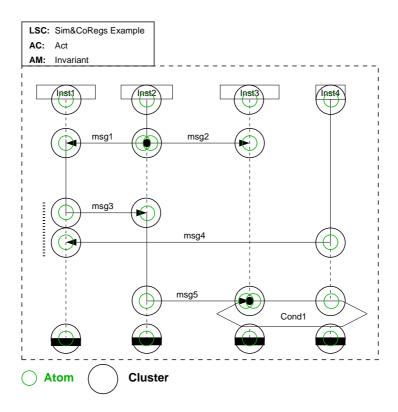

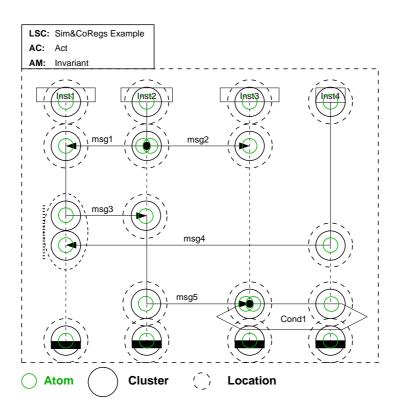

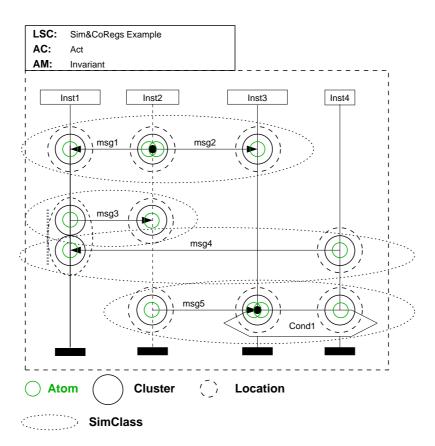

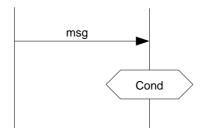

Figure 1.1: Symbolic Timing Diagram example

Using graphical notations to visualize temporal logic formula is the second method of simplifying the specification. Timing diagrams used in hardware design are the base for the first such graphical specification languages. Most interesting from our perspective are the *Symbolic Timing Diagrams* (STD) developed by Schlör, which first appeared in the early 1990's [SD93]. The definition of the semantics of LSCs presented in later chapters of this thesis has been influenced to a large degree by the semantics given for STDs in [Sch00]. STDs extend standard timing diagrams by allowing to specify qualitative time constraints between value changes (called *events*), of signals (called *waveforms*). Figure 1.1 shows an example STD with two waveforms, three events and one constraint. A later extension of STDs adds quantitative time constraints [Fey96, FJ97].

STDs are a state-based formalism, which are best suited for the specification of black-box requirements, i.e. consider only the external interface of a component, but also support compositional reasoning. Other approaches using timing diagrams as property specifications exist, e.g. [Kut94], [Fis99] or [AEKN00]. *Constraint Diagrams* [Die96] are a similar formalism, which allows real-time specifications and is based on the Duration Calculus.

# Specification of Communication Properties

The specification formalisms in the preceding section have been developed with a single component in mind. The expressivity of most approaches also allows to state properties about several components, but they are not tailored to this particular use case. With respect to the increasing number of embedded controllers, which are used today and which often also exchange information and commands among each other, an appropriate graphical formalism is needed in order to meet the changed demands. Ideally, such a formalism is not limited to being a graphical front-end for temporal logic, but is suited also for other use cases, as elaborated below.

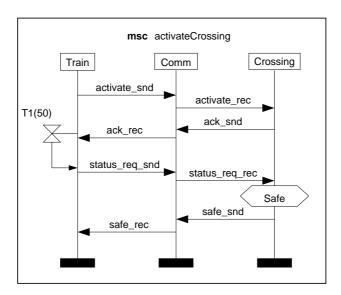

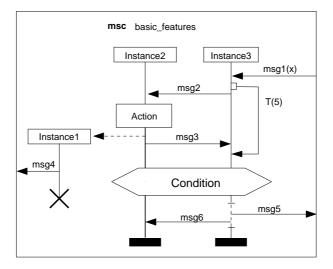

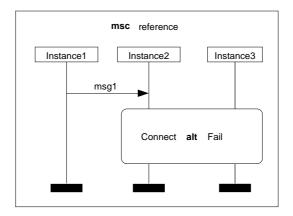

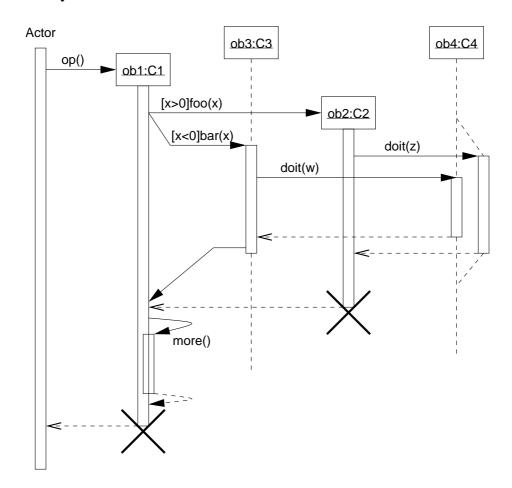

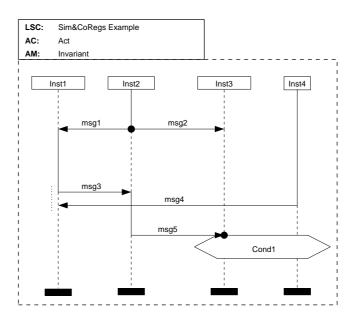

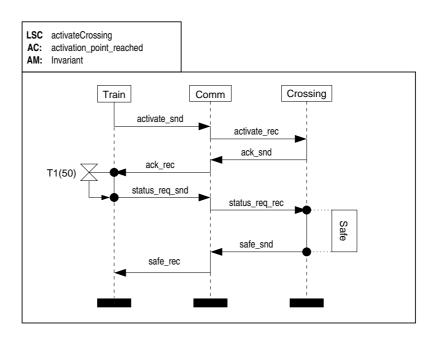

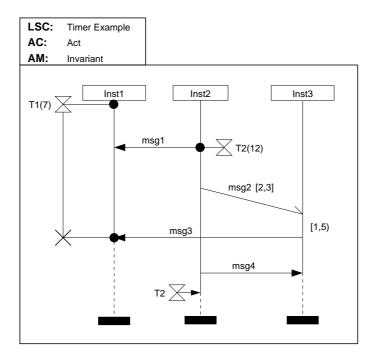

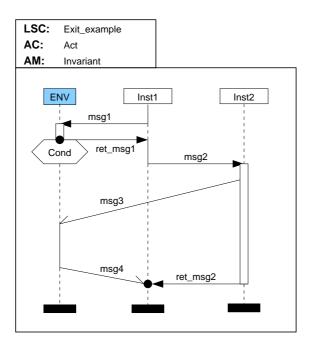

Figure 1.2: MSC example

Message Sequence Charts (MSCs) [IT93] have been used for specifying communication behavior for some time, predominantly in the development of telecommunication systems, and thus are a good candidate for such a formalism. Figure 1.2 shows an example for an MSC describing the message exchange necessary for the securing of a crossing. The three vertical lines, called *instances*, represent the communicating entities: the train, the communication channel and the approached crossing. Messages are depicted by arrows between the instances, the condition Safe indicates that the crossing is in a safe state, and the hour-glass symbol represents a timer.

This example demonstrates the intuitiveness of these basic MSC constructs, which motivates their application for the requirement capture in the early development phases, where they are used to document typical interactions, often referred to as *scenarios*. This is also the major use case for *Sequence Diagrams* (SDs), which are a very similar graphical description within the UML and are applied to the same end there. Today, such scenarios serve two purposes: gaining a better understanding of the behavior of the developed application, and documentation. They often also record simulation or test traces. More advanced use cases are conceivable, however, which reuse the early scenarios in later stages of the development process and thus provide an added value. The following use cases show great promise:

Model Synthesis Starting from a set of scenarios, which identify the entities comprising the system under design (SUD) and describe their typical interactions, a first cut of a model is synthesized. From the communication behavior shown in the MSCs or SDs a preliminary model structure and behavioral description is derived, which can be extended manually.

Existential Check Once a model exists it can be checked, if the functionality specified by the early scenarios is possible in the current model, i.e. if it is able to fulfill each behavior described in a scenario at least once. A failed check indicates a fundamental error. This check serves as an early and easy to use debugging aid.

Model Testing When a largely stable model exists and a simulator is available, MSCs/SDs can serve as watchdogs monitoring a user-driven simulation session. Deviations from the specified scenarios are detected and reported. Additionally MSCs/SDs can be used to *drive* the simulation without user interaction by providing the required input stimuli and observing, if the expected model reactions ensue. This use case is another step toward a reference model and is also ideally suited for regression testing, where a set of MSCs/SDs are re-run after a change to the model in order to ensure that the basic original functionality is still guaranteed.

**Formal Verification** MSCs/SDs can be used to state communication protocols between different entities and employ them for formal verification.

**Test Vector Generation** Existing scenarios from earlier phases in the development or also newly generated ones can be used to automatically generate test vectors for integration testing of several communicating embedded controllers.

All of the abovementioned use cases demand a formal foundation in order to be realized by corresponding tools. Neither MSCs nor SDs fully comply with this demand. For MSCs a formal semantics exists, but several important issues are covered only inadequately or not at all. Liveness properties, e.g. that a message must arrive at its destination, can for instance not be expressed in the formal semantics of MSCs. Only safety properties are expressible, i.e. that the receipt of a message may only occur after sending. For Sequence Diagrams no formal semantics has been defined so far. Moreover, both languages are lacking expressiveness wrt. to the envisioned advanced use cases. For the verification and model testing use cases e.g. it is vitally important to know when the specified communication behavior should be observed, i.e. when the chart is active. A more detailed introduction and criticism of MSCs and SDs in this respect is presented in chapter 3. A in-depth treatment of the state-of-the-art regarding the abovementioned advances use cases is given in the chapters dealing with the individual language constructs of LSCs.

In summary we can state that in general the intuitiveness and visual appeal of MSCs and SDs is very well suited for the abovementioned use cases, but they are lacking expressiveness and an adequate formal semantics. This is where Live Sequence Charts, the central subject of this thesis, come into play. Damm and Harel noted the potential of MSCs and SDs to become more than scenario descriptions, if given a sound and more expressive basis, and proposed Live Sequence Charts (LSCs) in [DH98] as an extension of MSCs and SDs, which addresses these shortcomings. This work is the starting point for the present thesis, where the basic ideas of Damm and Harel are rendered more precise and treated more completely than in [DH98].

The fundamental idea of LSCs is the distinction between *mandatory* and *possible* behavior, where conventional MSCs and SDs are considered as consisting of possible elements only and mandatory elements constitute the enhancements of expressiveness offered by LSCs. This concept is applied to almost all language constructs: entire charts, instance lines, messages, conditions, etc. On the chart level this allows the distinction between *existential* and *universal* LSC specifications, the former being the scenario view of MSCs

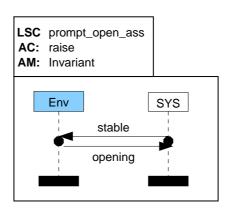

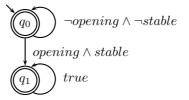

and SDs (there exists a run, which conforms to the chart) and the latter allowing the specification of protocols, which have to be obeyed by all runs of a system. For instance lines and messages mandatory means that liveness properties can be specified, i.e. points along an instance line must be reached and messages must be received once sent. This important feature is also the source of the name of Live Sequence Charts. The expressive power of LSCs is additionally enhanced by truly supporting conditions by associating them with a boolean expression (making them "first-class citizens" in the words of [DH98]), instead of the informal treatment in MSCs or their absence in SDs. Conditions in LSCs are not limited to single points in time, but may constrain a number of contiguous time points, in which case they are called local invariants. Additionally, LSCs allow to specify the activation point of a chart by an activation condition. The full set of features is explained in more detail in chapters 4 - 9.

The goal of this thesis is the development of a language for the easy, intuitive, graphical specification of interactions between communicating entities. This language are Live Sequence Charts. The first task in this respect is the definition of the language constructs required to express the properties necessary for a more prominent role of sequence charts<sup>4</sup> in the development process. This involves a non-trivial trade-off between retaining as much intuitiveness as possible on the one hand and providing as much expressive power as necessary on the other. The second major task is the definition of a suitable formal semantics, which unambiguously expresses the meaning of all features and their combinations and thus allows the automated processing of LSCs.

Another point is essential in order to successfully apply any formalism or method in general, and LSCs in particular, in the real world: An indication has to be given in which phases of the development the formalism in question should be applied and to which end. Answering this question is the third goal of this thesis. The final task is the evaluation of the LSC language by applying it to one of the abovementioned advanced use cases: formal verification. The evaluation should demonstrate, if the expressiveness is sufficient and if the semantics is appropriate and useful in practice. This proof of concept will be done by using LSCs for property specification for the formal verification of STATEMATE designs.

$<sup>^4\</sup>mathrm{We}$  will use the term 'sequence chart' to denote the sum of all dialects, be it MSCs, SDs, LSCs, . . . .

# Formal Verification of Statemate Designs

This section briefly introduces the Statemate tool and notations and also gives a short overview over the Statemate Verification Environment (STVE), into which the tools dealing with LSCs are prototypically integrated.

## Statemate

STATEMATE is a CASE-tool, distributed by I-Logix, Inc., USA, which allows to build an abstract model of an SUD, e.g. an embedded controller. It offers to capture several views onto the SUD, the most important ones being the functional decomposition and the behavioral description. Other views like the modeling of continuous aspects or physical distribution of components are possible as well; the details are described e.g. in [HLN<sup>+</sup>90] or [HP96]. Here only the former two aspects are explained as the STVE is based on these.

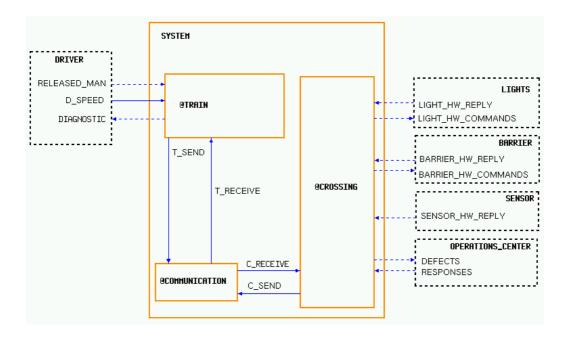

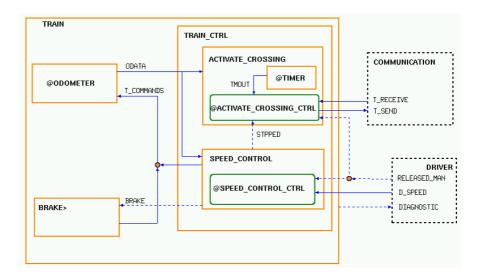

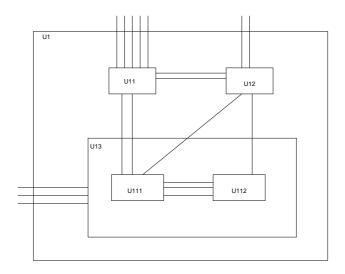

Figure 1.3: Top level Activity Chart

#### **Activity Charts**

The functional decomposition of an SUD is modeled by Activity Charts, whereas the behavioral description is given by Statecharts. Figure 1.3 on the preceding page shows an example for a top-level Activity Chart for the train control system, which is discussed in more detail in chapter 2. Each functional unit, called activity in Statemate, is represented by a solid line box, e.g. TRAIN or CROSSING in figure 1.3. The environment is represented by external activities depicted by dashed line rectangles, e.g. DRIVER or BARRIER, which provide input stimuli or accept outputs of the model. Activities can be structured into a hierarchy, where each Activity Chart represents one level of the hierarchy. The top-level Activity Chart in figure 1.3 for instance contains the three activities shown, which in turn are further decomposed into other Activity Charts, indicated by the '@' in front of the activity name. The activities TRAIN and CROSSING are truly decomposed further as shown in figures 2.3 on page 28 and 2.10 on page 37 in section 2.2, whereas the Activity Chart for COMMUNICATION contains only the behavioral description of this component.

On each level of hierarchy a *control activity* can be specified, which is responsible for controlling, i.e. starting, stopping, etc., the other activities present. The control activity is depicted by solid line box with rounded corners (e.g. SPEED\_CONTROL\_CTRL in figure 2.3 on page 28). If no control activity is specified, as is the case in the Activity Chart in figure 1.3, all activities at this level of hierarchy are activated at system start. A control activity located on a level without any other activities, e.g. SPEED\_CONTROL\_CTRL, is one of the possibilities offered by STATEMATE for the specification of behavior.

Information exchange between activities is depicted by arrows leading from the sender to the receiver. The user can distinguish *data* and *control flows*, represented by solid, resp. dashed arrows. Several individual communications leading from one sender to the same receiver can be combined into a single arrow, called an *information flow*.

#### Statecharts

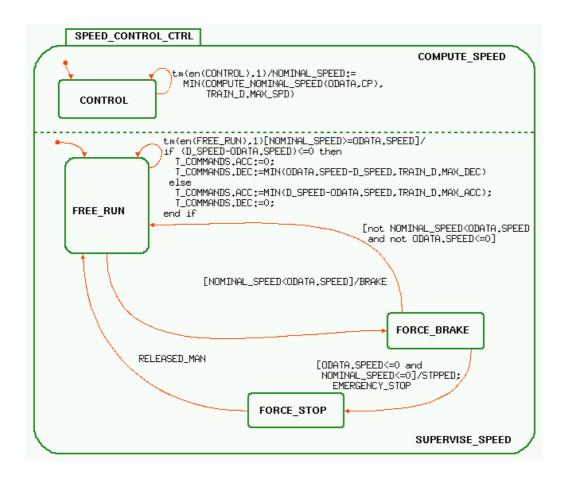

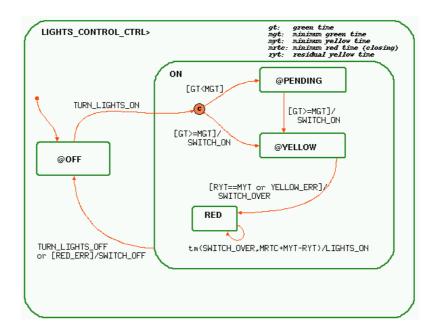

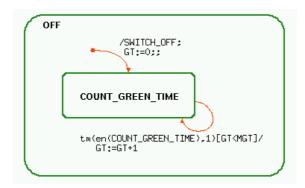

STATEMATE offers several concepts for the specification of the behavior of an activity. The most important one are Statecharts [HP96, HN96], which can be roughly characterized as automata extended by parallelism and hierarchy. Figure 1.4 on the facing page shows an example for a Statechart,

Figure 1.4: Statechart example

again taken from the model of the train control system. The Statechart SPEED\_CONTROL\_CTRL is split into two parallel parts, called *AND-States* in STATEMATE terminology, indicated by the dashed line separating sub-states COMPUTE\_SPEED and SUPERVISE\_SPEED. The latter is further structured into three sub-states, so-called *OR-states*. States, which are not decomposed, are called *basic states*. All sub-states of an AND-state are active, when the governing AND-state is active, i.e. both COMPUTE\_SPEED and SUPERVISE\_SPEED are active when SPEED\_CONTROL\_CTRL is active, whereas only exactly one of the OR-states at each level of hierarchy may be active at a time, i.e. if SUPERVISE\_SPEED is active either FREE\_RUN or FORCE\_BRAKE or FORCE\_STOP is active. The entire Statechart is active, if the activity it is contained in is active.

When a Statechart is active it can react on changes to system variables by taking transitions between states. Each transition is annotated by

### trigger[guard]/action

consisting of a trigger, which determines when the transition is possibly enabled, a boolean expression guard, which further restricts the enabledness of the transition, and an action part containing the ensuing consequences. A transition is enabled, if the source state is active, the trigger is observed and the guard evaluates to true. An enabled transition need not fire, since there may be other transition, which are enabled concurrently. There are priority rules determining which enabled transition is actually fired, but not all cases can be covered by these rules, so that non-deterministic situations can arise. If a transition is fired, control changes to the target state and the actions are executed, which can consist of the generation of events, variable assignments, control commands for other activities, e.g. st!(TIMER) or sp!(TIMER) for starting, resp. stopping activity TIMER.

Which state of a Statechart or decomposed state is active initially is determined by a *default transition*, which is graphically depicted as a transition without a source state; state FREE\_RUN e.g. is initially activated in figure 1.4.

Variables in STATEMATE are typed and the user may choose from several data types, one of the most important ones being Event, which is a boolean signal visible for one *step* (execution cycle). Other available types are *condition* and *data items*, the latter comprising integer, real, etc.; see [HP96] for more details. Other modeling constructs will be introduced by example when presenting the STATEMATE for the train control case study in section 2.2.

#### **Statemate Simulation Semantics**

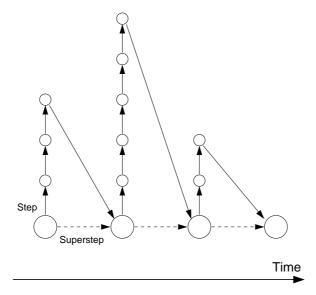

Part of the Statemate tool is a simulator, which allows the interactive execution of the model. Simulation runs can be recorded in *Simulation Control Programs* (SCP) to be replayed later. The simulator supports two execution models: *synchronous* and *asynchronous semantics*, which differ in the underlying time model and the points in time when the embedded controller communicates with its environment.

In the synchronous semantics the model accepts inputs from the environment every step, whereas in the asynchronous semantics new inputs are consumed only when all computations in reaction to the previous inputs have been completed, i.e. a stable state is reached, where no further transition can

be fired without new input stimuli. In the asynchronous semantics reaction to one set of input stimuli thus may entail several internal steps, which do not consume time; time only passes when the system has reached a stable state and synchronizes with its environment. The transition from one stable state to the next is called a *superstep*. The asynchronous semantics is often also referred to as *superstep semantics*, the synchronous one as *step semantics*.

#### Statemate Verification Environment

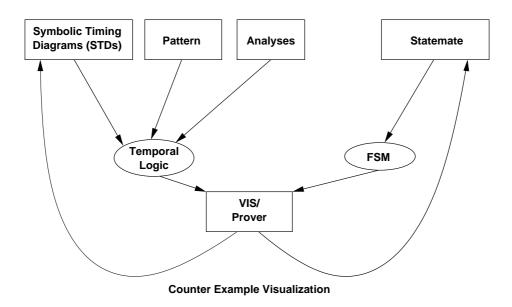

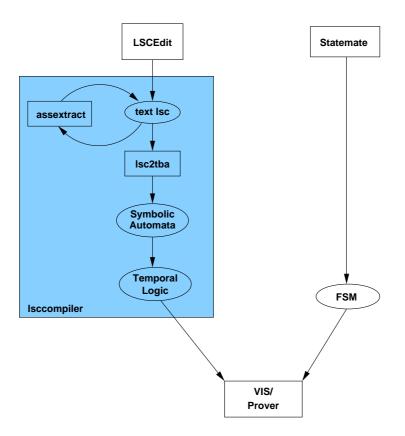

Figure 1.5: Overview over the Statemate Verification Environment

The Statemate Verification Environment (STVE) has been developed jointly by the embedded systems division at OFFIS e.V.<sup>5</sup> and the University of Oldenburg in order to provide easy to use formal verification capabilities to users, which have no intensive training in formal methods. Part of the techniques and formalisms described in the remainder of this section form a commercial product offering, which is marketed by OSC Embedded Systems AG, Oldenburg, Germany, and I-Logix, Inc., USA. This section gives an overview over the techniques integrated in the commercial product and also other concepts, which are currently not part of the product. We subsume the

$<sup>^5</sup>$ Oldenburger Forschungsinstitut für Informatikwerkzeuge und -systeme

entire set of features and techniques under the term Statemate Verification Environment. Figure 1.5 on the page before shows the general organization of the STVE.

The offered techniques are grouped into different skill levels ranging from analyses, which can be employed by ordinary designers familiar with STATE-MATE to full-fledged property specification and verification capabilities. The increase of expert knowledge required is accompanied by an increase of expressive power: the more knowledge is needed to apply a technique, the more complex properties can be expressed.

The techniques offered are grouped into three categories: robustness checks, pattern-based verification and STD-based verification. The robustness checks are simple, but formal analyses, which can be used by a typical STATEMATE user. They comprise checks/analyses for

#### • non-deterministic situations:

- concurrently enabled transitions

- multiple writer (two or more activities simultaneously write a data item)

- read-write hazards (a data item is read and written simultaneously)

- range violations (a data item is assigned an out-of-range value)

#### reachability

- reachability of basic states

- reachability of state configurations (sets of basic states)

- reachability of transitions

- reachability of specific values for data items

Note that the check for a non-deterministic choice between concurrently enabled transitions only reports those situations, which are not already resolved by the Statemate priority rules for transitions. These analyses are intended to be used for debugging purposes as the model is developed by answering questions like: "Are all states of the model reachable?", "Is it possible to observe value '7' at output o1?", or "Are there situations, where —

after applying the priority rules — more than one transition is concurrently enabled?".

There are two core verification engines which can be used alternatively: the VIS model checker ([Gro96a, Gro96b]) and a bounded model checker based on the SAT checker ProverCL. By exploiting the counter example generation capabilities of the VIS witnesses are produced, which lead into exactly those situations, which have been checked by the robustness analysis, provided such a situation exists. The general goal of these analyses thus is falsification, i.e. the expectation is that a witness exists, e.g. how to reach a certain basic state. This can be exploited by using reachability-based model checking with early termination<sup>6</sup> [Gro96a, Gro96b]. Instead of employing the standard backward-oriented fix-point iteration (see e.g. [CGP99]) this strategy checks the formula while performing a forward-oriented reachability analysis. If the formula does not hold, the reachability analysis is aborted (early termination), because a counter example has been found. If the formula indeed fails, this strategy generally performs better than the fix-point iteration, since only part of the reachable states need to be considered.

Falsification is also the prime use case for the practical application of bounded model checking [BCCZ99], which is very efficient for these cases. When a checked property does not hold, SAT-checkers, which form the core of bounded model checkers, are typically more efficient than standard model checkers. The STVE therefore offers bounded model checking via integration of the SAT solver ProverCL [SS98] of Prover Technologies, Sweden, instead of the VIS for robustness checks and other situations when a counter example is expected. Note that both reachability-based and bounded model checking are limited to check invariant formulas of the form ' $\mathsf{AG}(p)$ '.

More information on the robustness checks of the STVE are found in [BBHW00, BDW00, OSC02b, BDKW01].

The pattern-based verification is a oriented towards certification, instead of falsification, i.e. the specified properties are expected to hold on the model. The STVE offers a library of pre-defined parameterized patterns, which allow to express a set of typical properties. Each pattern is instan-

<sup>&</sup>lt;sup>6</sup>The term "reachability" used here is a different one than the one used in the above checks. The term here refers to reachable states in the finite state machine (FSM) generated for the Statemate design, whereas reachability as used above refers to Statemate items (basic states, transitions, etc.).

<sup>&</sup>lt;sup>7</sup>The bounded model checking procedure described in [BCCZ99] also considers other formulas, but in practice globally formulas are used almost exclusively.

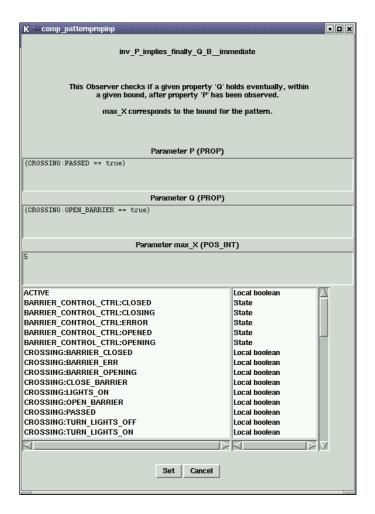

Figure 1.6: Pattern instantiation example

tiated by supplying concrete STATEMATE expressions. An example pattern is e.g. P\_implies\_finally\_Q\_B, which can be used to express the property "After the train has passed the crossing, the command for the opening of the barriers must be given within 5 steps.". Figure 1.6 shows the parameter instantiation dialog for this property. The signal from the pass sensor is mapped to P, the open command for the barrier is mapped to Q and B, the upper bound for the time passed between the two signals, is mapped to 5.

The expressive power of this approach is on the one hand limited by the pre-defined set of patterns and on the other hand by the fact that the patterns for efficiency reasons have been designed to be used with the reachability-

based method. This entails that, in addition to safety properties, bounded liveness properties may be expressed as the example pattern demonstrates, but no unbounded liveness requirements.

More information on the STVE patterns is available in [OSC02a].

If more flexibility in stating requirements is desired or unbounded liveness properties are to be expressed, Symbolic Timing Diagrams (STDs [Sch00, FJ97]) are offered, which allow to specify completely user-defined properties. Figure 1.1 on page 6 shows an example STD, which has been specified for the crossing component of the train control system. The requirement is formulated over the interface objects CROSSING\_SAFE\_REC\_F and PASSED\_XING\_F and expresses that the crossing may only be passed by the train after it has indicated its safe state. Properties stated as STDs are checked using the standard fix-point iteration-based model check algorithm. More information on the application of STDs within the STVE can be found in [BW98, BBD+99, DDK99, KM00, DK01].

The overview shown in figure 1.5 on page 15 illustrates the general organization of the STVE. The STATEMATE design to be verified is transformed automatically into a finite state machine (right hand side of figure 1.5) and the property to be checked is translated into a temporal logic formula (left half of figure 1.5). The translation of STDs is split into two phases: first a symbolic automaton is derived for an STD, which in turn is transformed into a temporal logic formula.

If a property specified as an STD or pattern is violated by the model or a witness for a robustness check is found, the (bounded) model checker generates an error path, which can be visualized and examined in two ways. The preferred and most natural way is to translate it into an SCP in order to execute in the STATEMATE simulator. Alternatively the error path can be visualized as an STD.

For more information about the different formalisms and techniques contained in the STVE the reader is referred to the following references: [Bro99] describes the FSM generation for STATEMATE designs, [BDW00, BDKW01, BBHW00, OSC02b] provide more details about the analyses, the pattern-based approach is described in [OSC02a], and information on formal verification of STATEMATE designs using STDs can be found in [BW98, DDK99, KM00, DK01]. Details about the technologies underlying the STVE are contained in [BBD+99, BBB+99, Bie03, Wit03].

## Organization of this Thesis

Chapter 2 introduces the train control case study, which serves as a running example throughout this thesis. This case study deals with a radio-based signaling system for the control of level crossings. This chapter contains a general introduction and a detailed description of the Statemate model, which will also be used for obtaining experimental results in chapter 11.

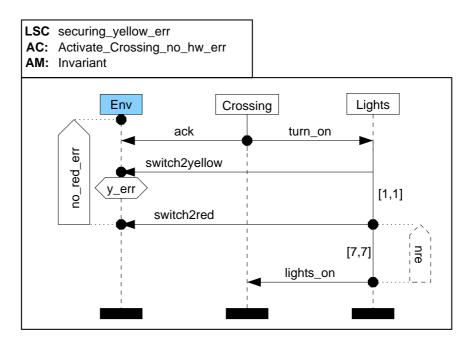

The language of Live Sequence Charts is motivated by both the visual appeal and lack of expressiveness and formal rigor of Message Sequence Charts and UML's Sequence Diagrams as has been expounded above. Chapter 3 gives an overview over the two sequence charts dialects, describing the major features, historical development and discussing the shortcomings wrt. the advanced use cases briefly presented above. The complete set of features of the LSC language, along with the definition of the formal semantics, is presented incrementally in the following chapters. Chapter 4 begins with the basic LSC features, whose motivation, graphical representation and informal meaning are described.

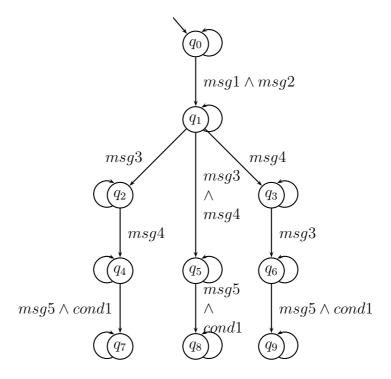

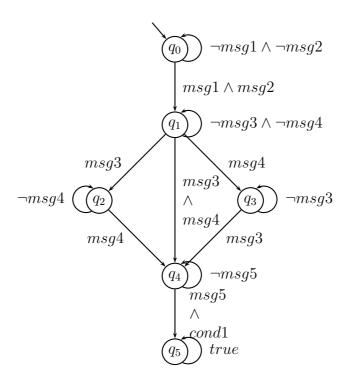

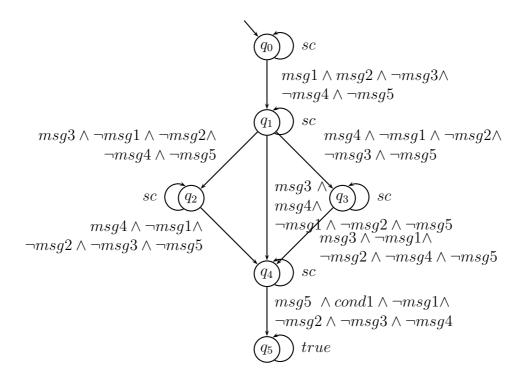

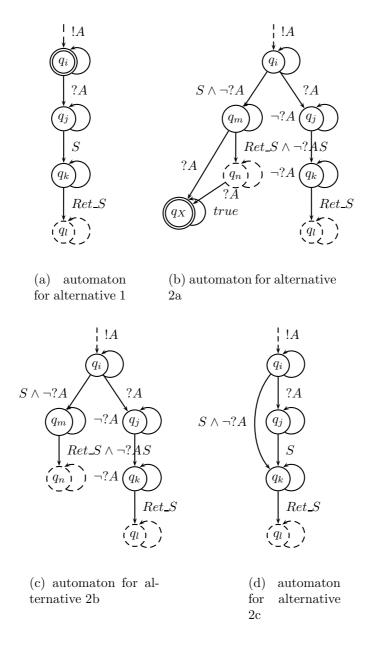

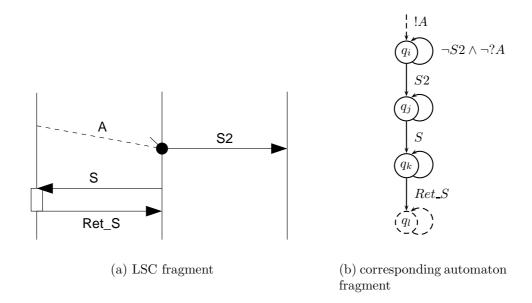

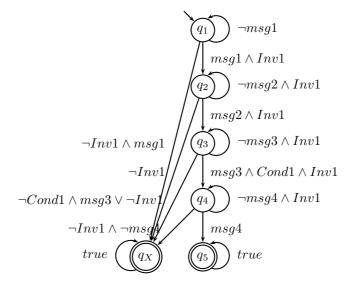

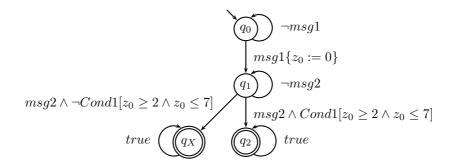

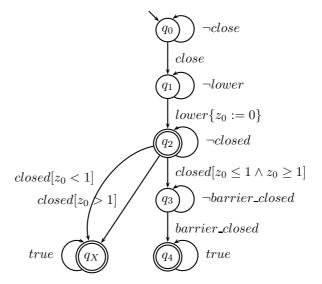

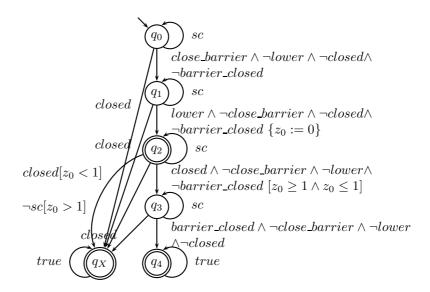

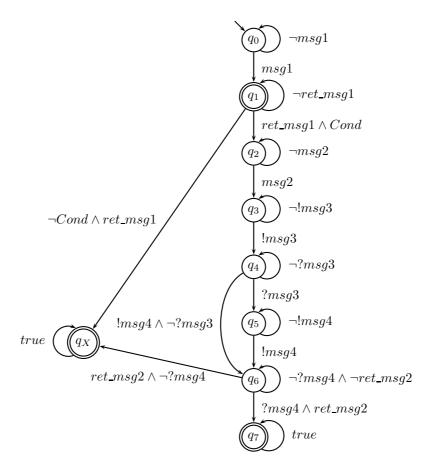

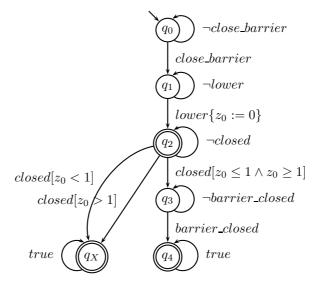

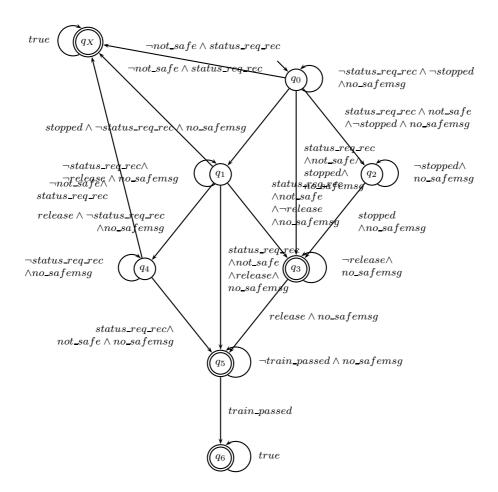

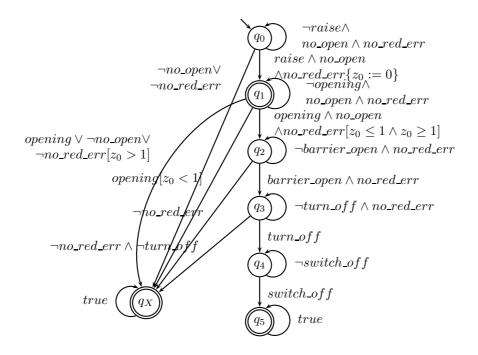

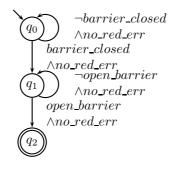

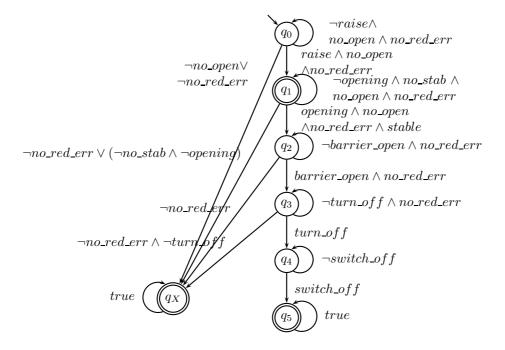

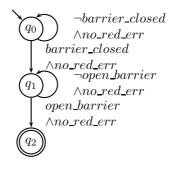

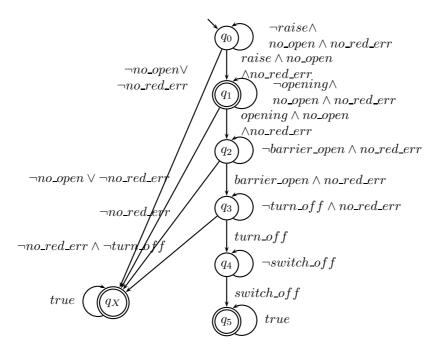

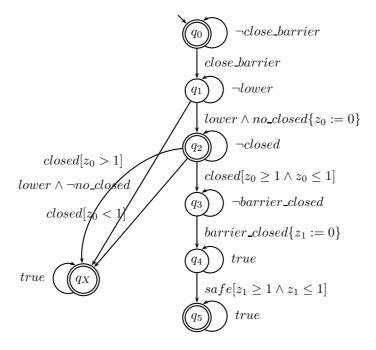

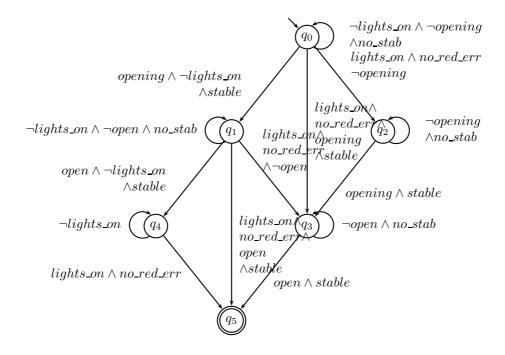

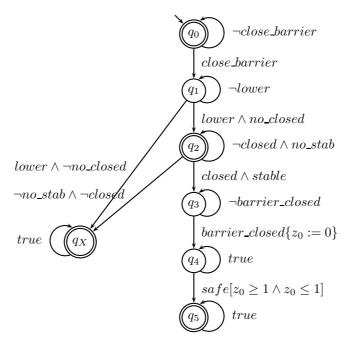

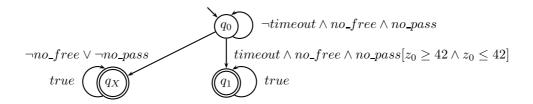

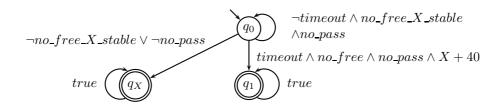

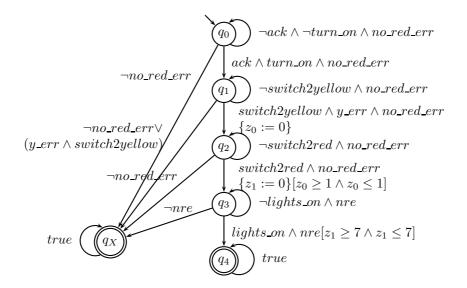

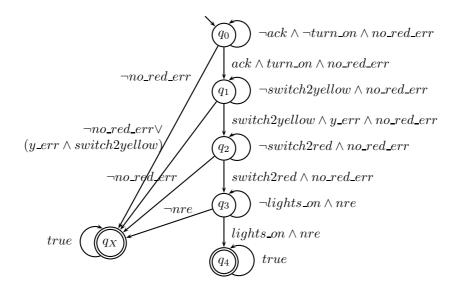

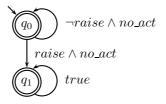

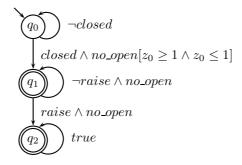

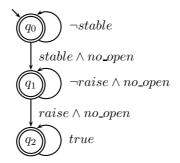

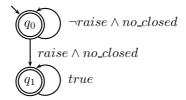

The semantics of an LSC is defined in terms of an automaton. The relation between the embedded controller being developed (the SUD) and the LSC specification is established by considering runs of the system and determining, if they are accepted by the automaton. The SUDs, whose properties are to be specified by LSCs, operate for an indeterminate amount of time (theoretically forever), so that the automata used for the semantics definition must be able to deal with infinite runs. Chapter 5 introduces a suitable automata format, derived from  $B\ddot{u}chi$  automata and also defines a corresponding timed variant thereof. Defining the semantics of LSCs in terms of Büchi automata allows to easily derive temporal logic formulas due to the well-known relationship between (a sub-class of) Büchi automata and LTL. The temporal logic formulas are essential for later formal verification activities.

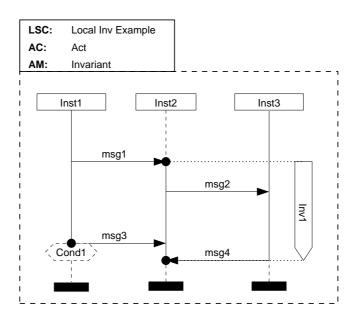

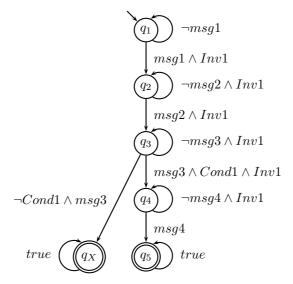

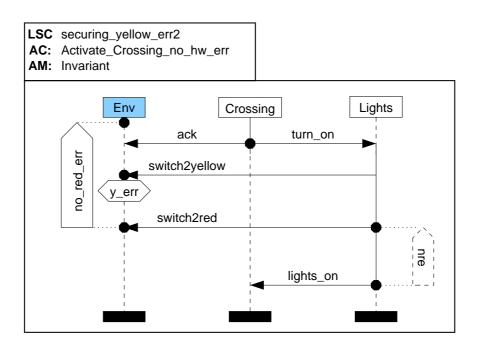

Chapter 6 defines a formal syntax for the LSC constructs introduced in chapter 4, upon which the algorithm for the generation of the automaton operates. The basic algorithm defined here is extended in the following chapters. The complete semantics of an LSC is then defined on the basis of the generated automaton incorporating the activation and quantification information.

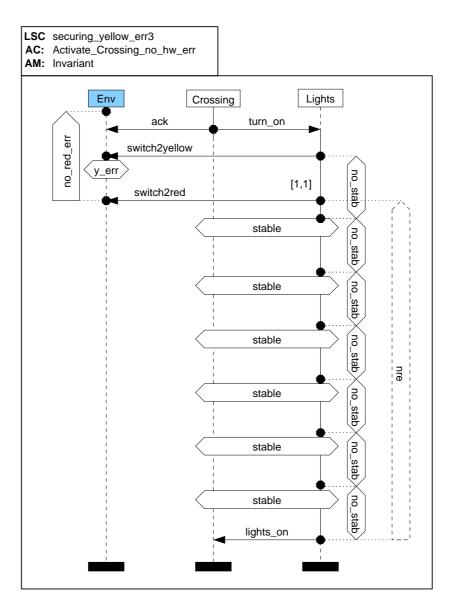

Chapter 7 extends the basic features by additionally considering timing constraints and extending the automaton generation algorithm to produce

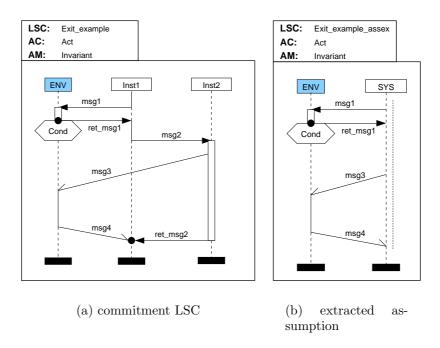

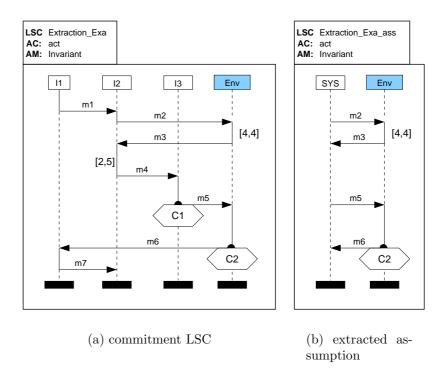

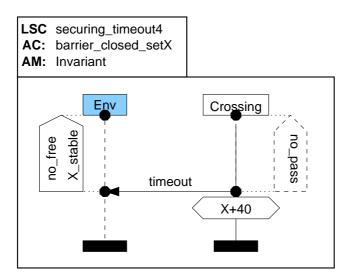

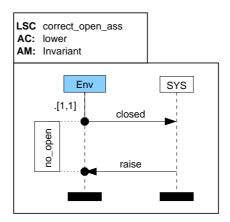

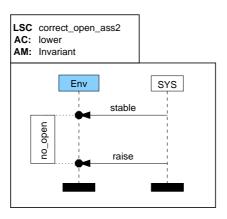

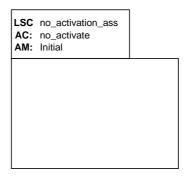

a timed automaton. Chapter 8 deals with a feature, which is essential for the use case of formal verification: assumptions. Since the environment of an SUD is already part of the LSC, in form of one or more environment instances, assumptions about the expected environment behavior are easily specified within an LSC by using elements on dedicated instances.

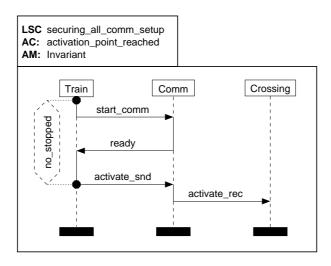

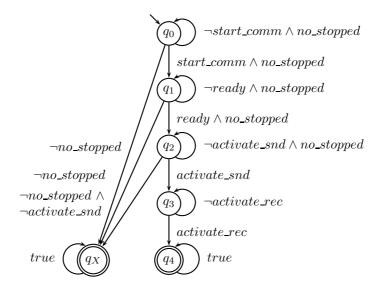

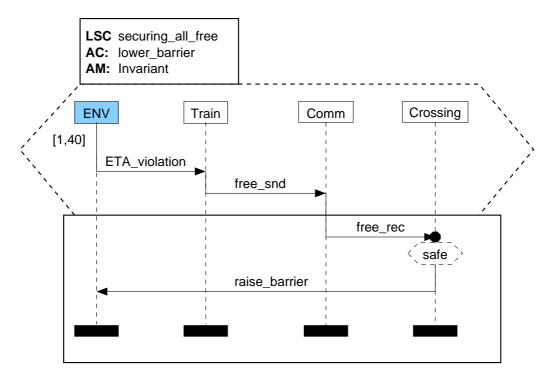

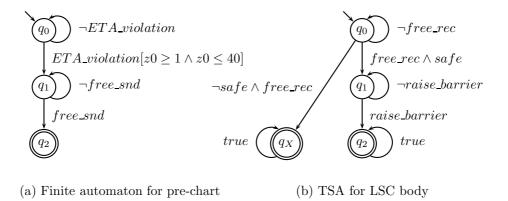

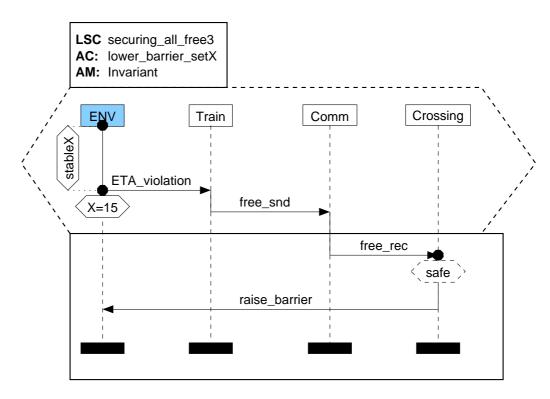

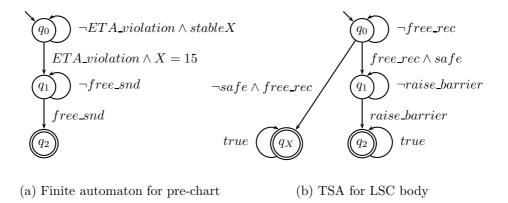

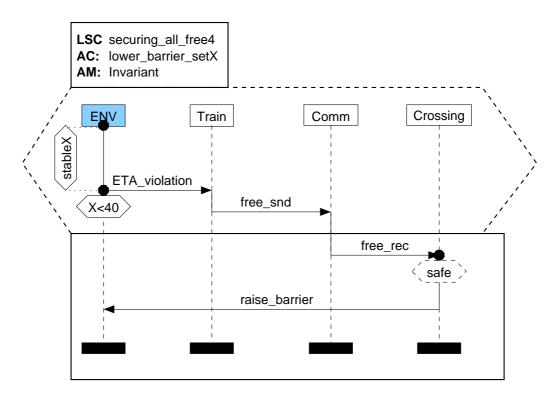

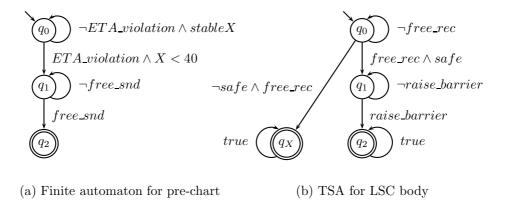

Chapter 9 enhances the activation information not only allowing to consider one point in time, via the activation condition, in order to determine if an LSC is to be activated or not. Additionally a sequence of messages forming a *pre-chart* may now trigger the activation of the actual LSC. The pre-chart semantics is again defined in terms of an automaton.

Chapter 10 addresses the third task specified above and proposes a methodology of how LSCs can be embedded into a model-based development process. The focus is on a re-use of LSCs from early stages in the design process.

The practical application of LSCs to the use case of formal verification is presented in chapter 11. The Statemate Verification Environment is covered in more detail and the integration of the LSC tools is described. The major part of this chapter is taken up by the experimental results. Chapter 12 concludes this work with a summary and identification of directions for future work.

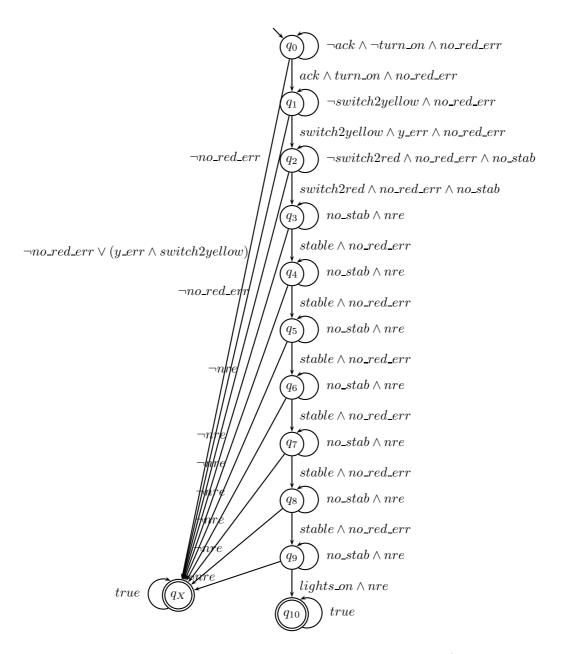

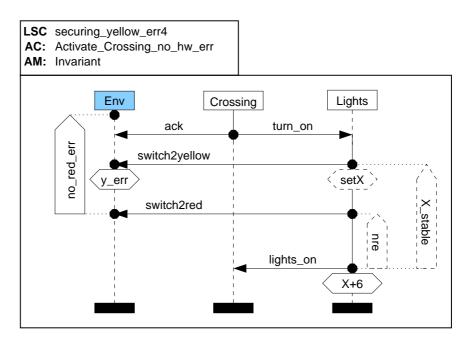

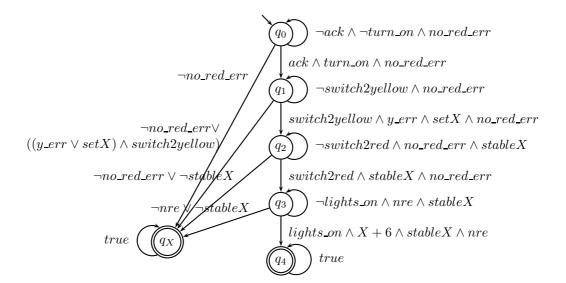

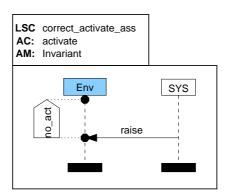

Appendix A summarizes all LSCs used in the verification of the train control system, including the corresponding automata. Appendix B lists the contents of all information flows used in the STATEMATE model for the train control system and appendix C contains the grammar of the textual LSC representation.

# Chapter 2

# Sample Application: A Radio-based Signaling System

This chapter introduces the case study, which will be used as a running example throughout this thesis. Section 2.1 gives a short introduction to the general subject before the STATEMATE model of the case study is presented in section 2.2. This STATEMATE model will also be used to evaluate the concepts and tools described in the remainder of this work; cf. chapter 11.

# 2.1 General Description

The control of level crossings, crossings for short, is currently carried out by wayside hardware, for example sensors, which announce an approaching train to a crossing, signals, which for instance indicate the status of the crossing to the train driver, etc. This solution is rather inflexible, since the hardware is permanently installed and must be able to handle different trains varying in speed, length, etc. Another drawback is the high amount of maintenance involved to keep signals, sensors and wiring operational. International rail traffic additionally raises demands for more flexibility, since almost every European country uses different signaling technology, so that trains can not easily cross borders. This has prompted railway companies to look for better, more flexible and efficient solutions for the control of trains, crossings, etc. There exist efforts on the European level with the objective of harmonizing and facilitating international rail traffic in Europe: the ERTMS/ETCS (European Rail Traffic Management System/ European Train Control System)

will use radio transmission, among other measures, for the communication between trains and the operations center (then called *radio block controller*). The German railway company Deutsche Bahn investigated a more advanced concept, which proposes to use a radio connection also for the communication between train and crossing and points. This allows more flexibility inasmuch as each train can contact a crossing depending on its specific information, a slow train would e.g. announce itself later than a faster train. This solution also entails lower maintenance effort, since the involved components are located on the train and directly at the crossing, instead of being dispersed along the track.

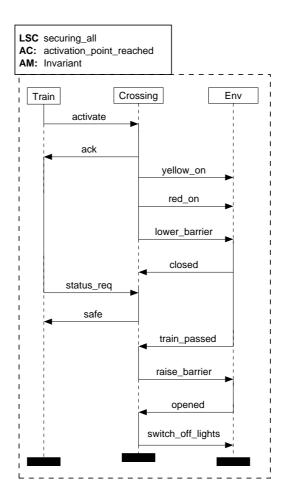

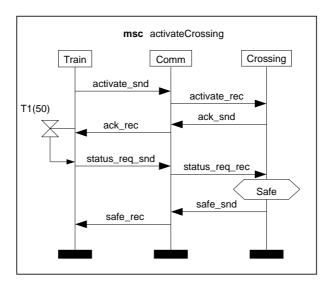

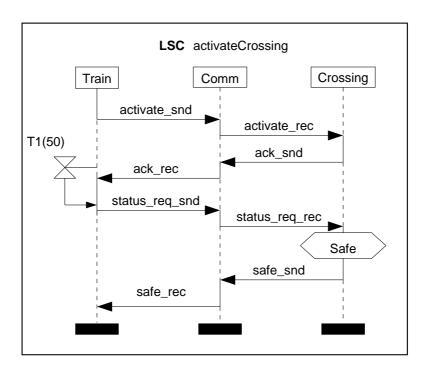

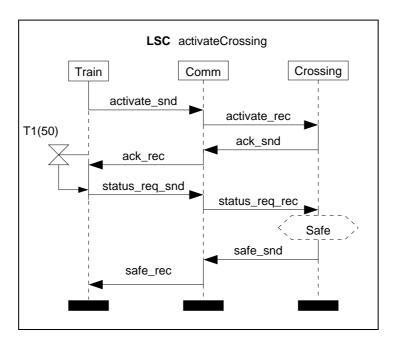

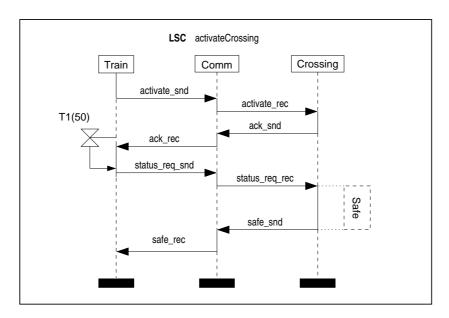

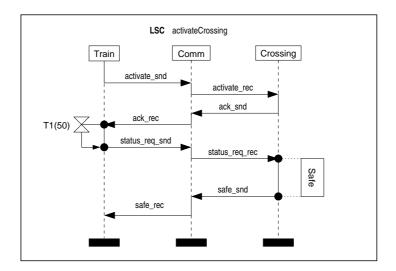

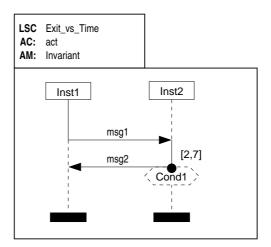

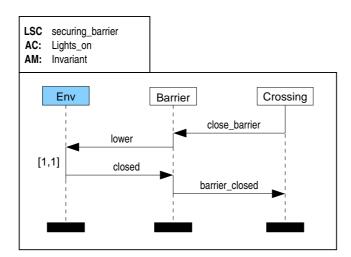

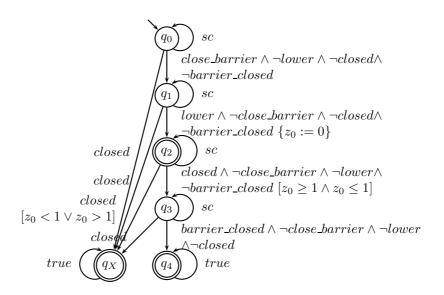

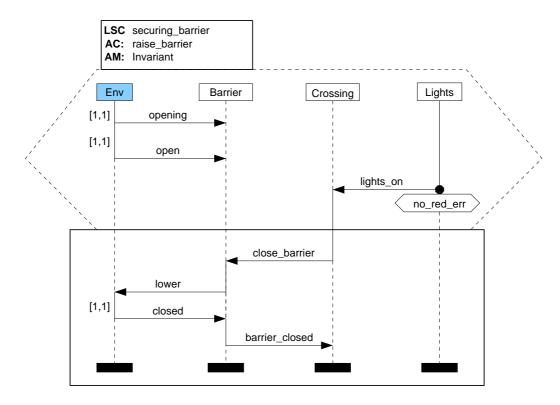

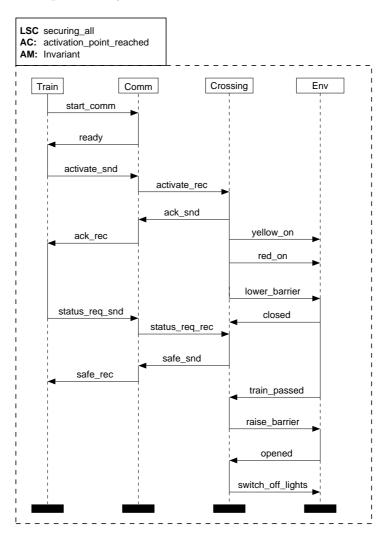

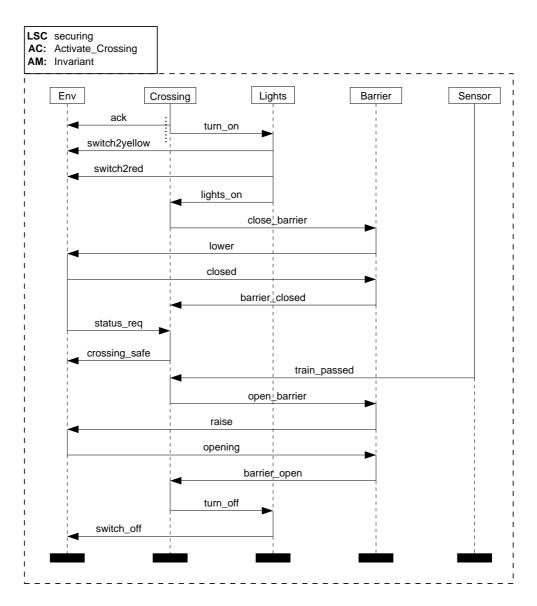

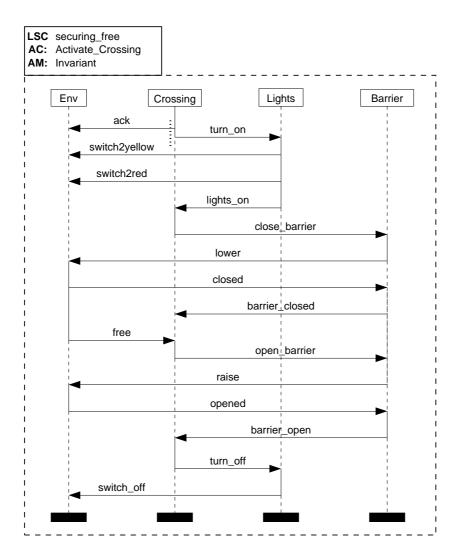

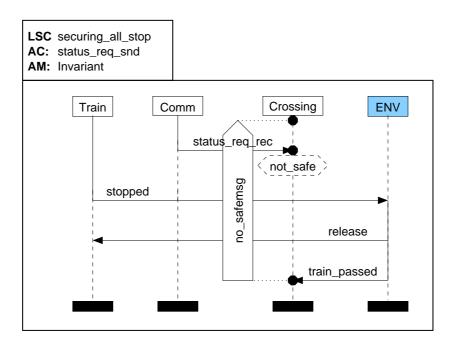

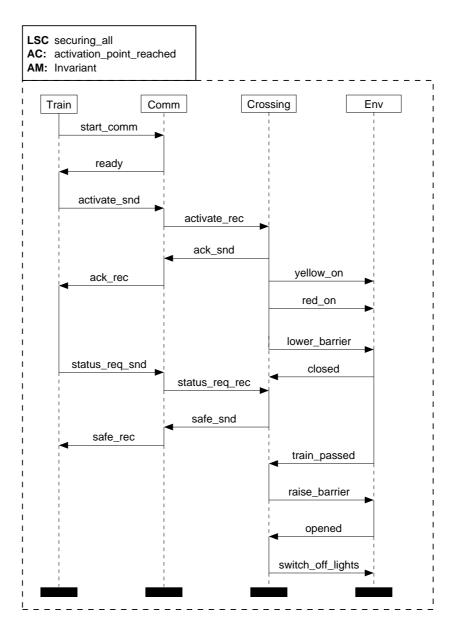

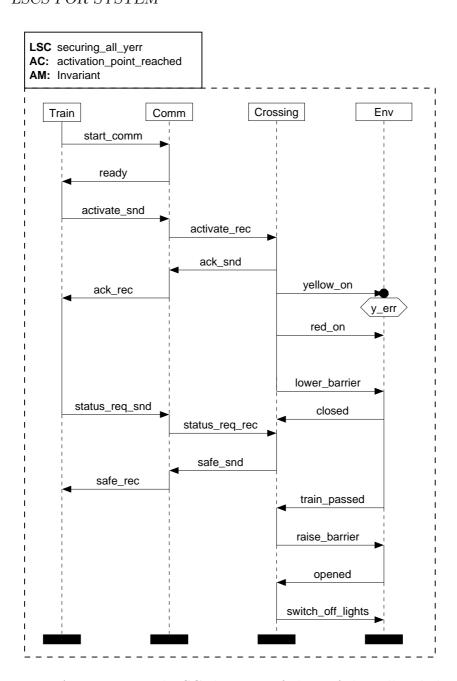

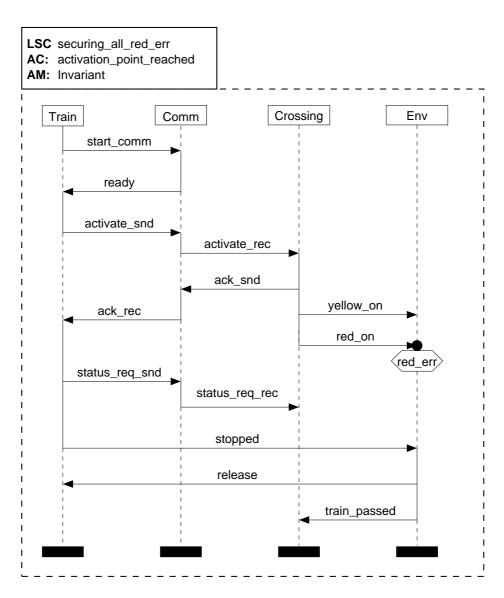

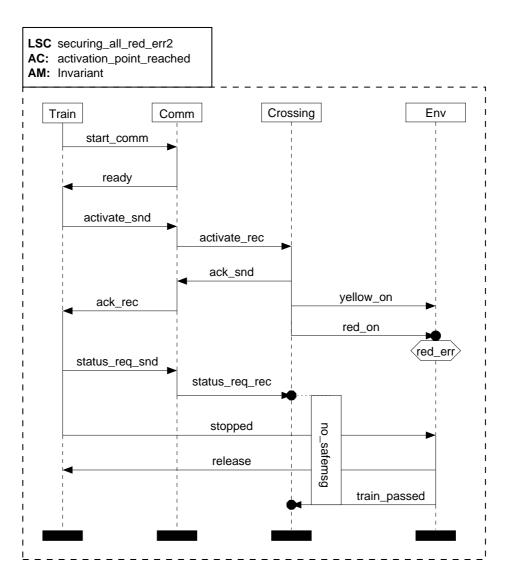

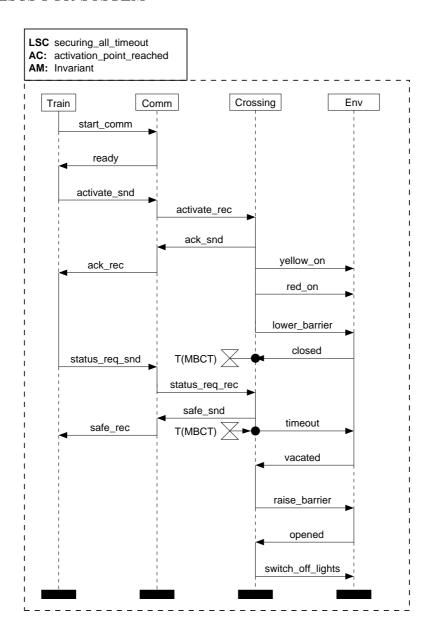

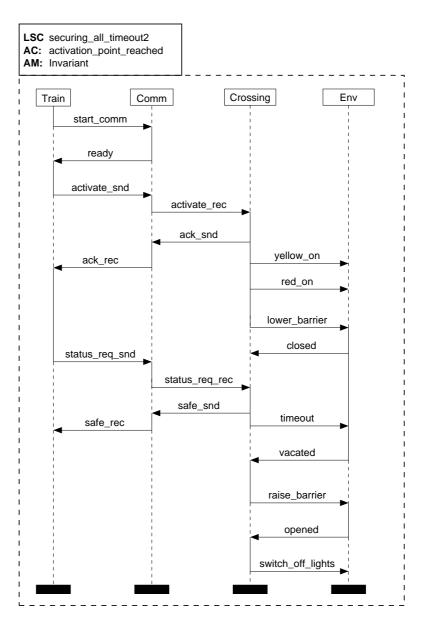

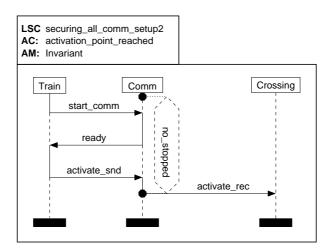

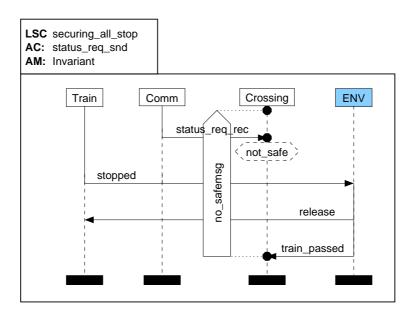

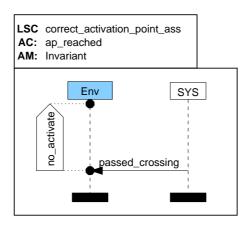

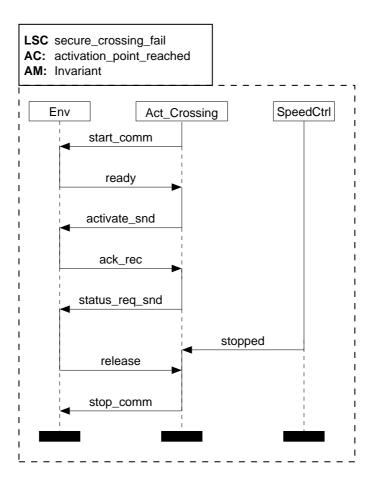

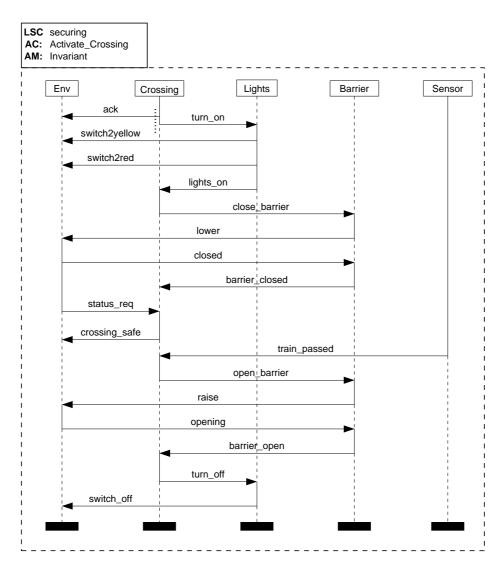

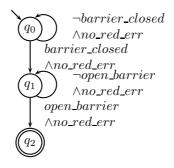

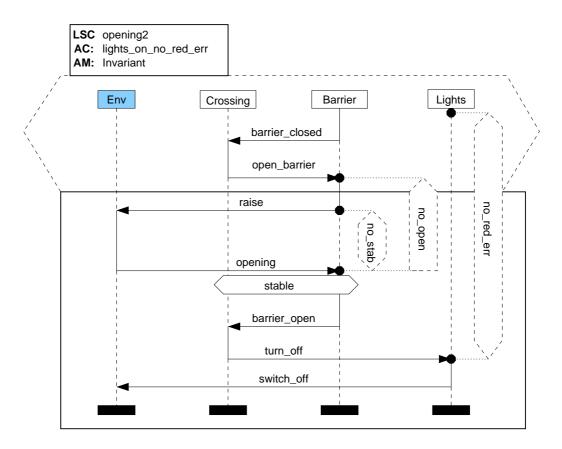

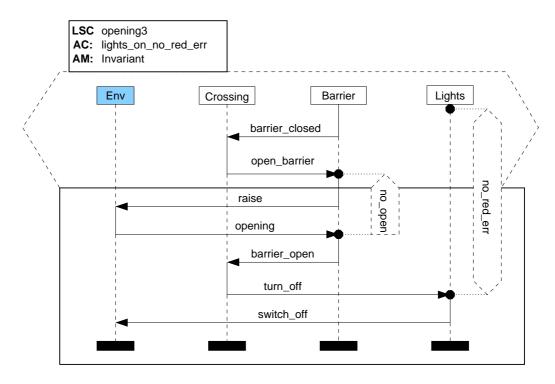

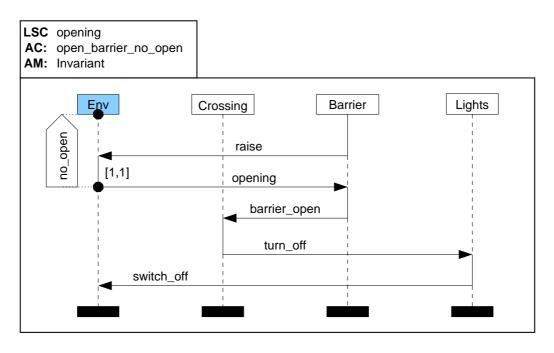

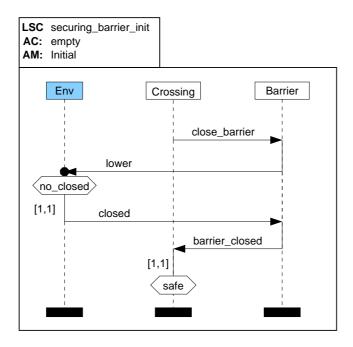

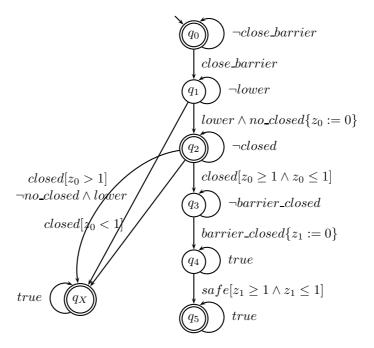

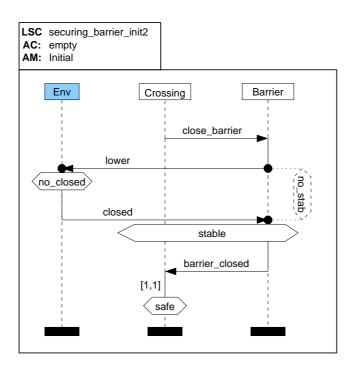

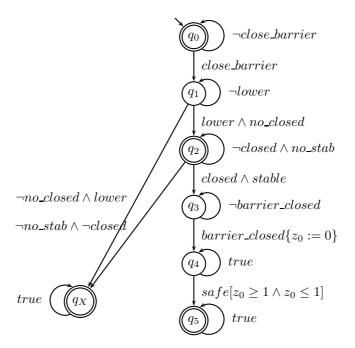

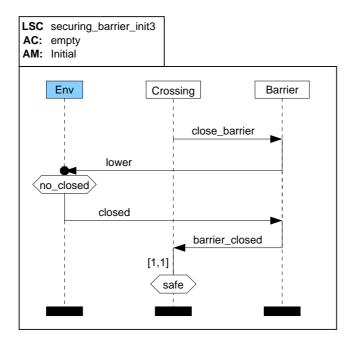

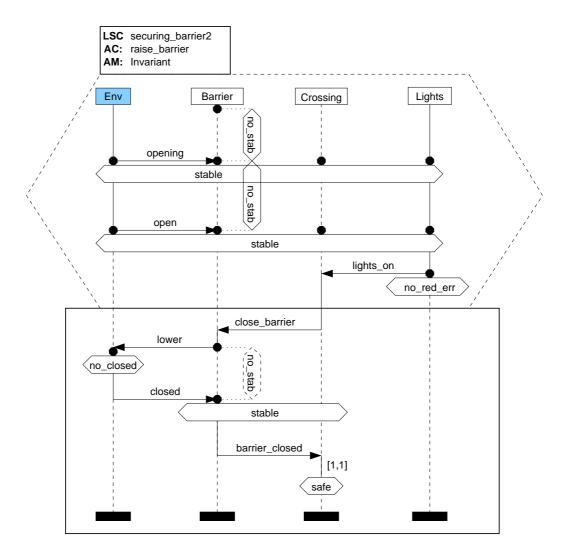

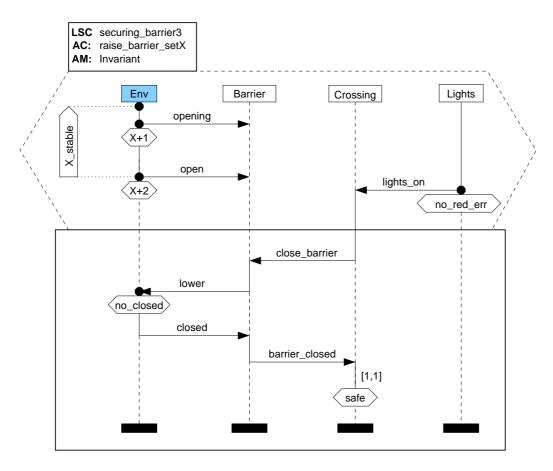

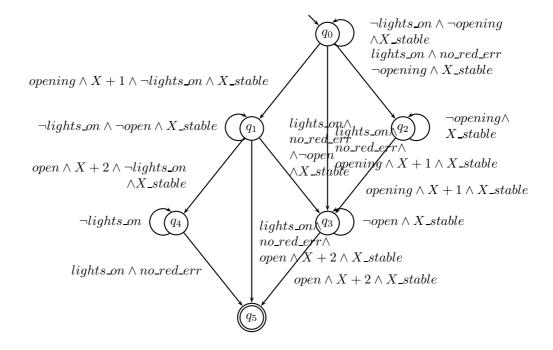

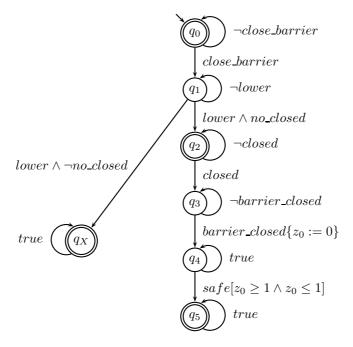

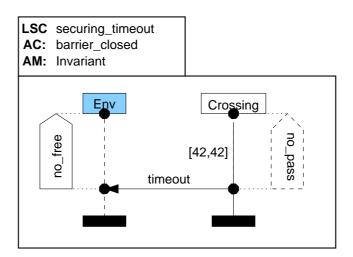

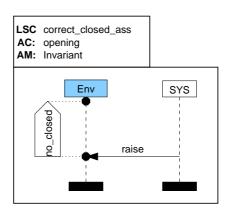

Figure 2.1: Existential LSC showing the typical interaction between train and crossing

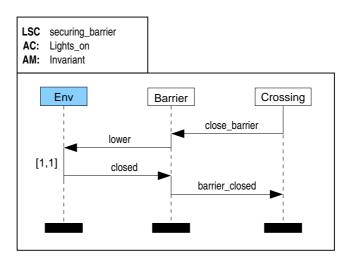

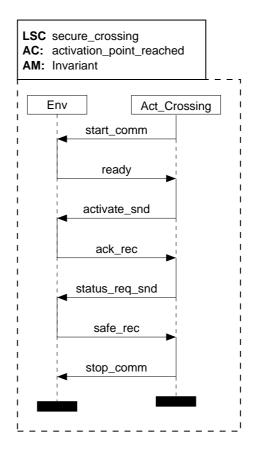

There are several different strategies used in the traditional control of crossings by means of wayside equipment, which serve as blueprints for the radio-based approach. This case study considers the radio-based crossing control according to the *guarding signal* strategy. Figure 2.1 shows an existential LSC depicting the typical interaction between train and crossing for this strategy. Even without a detailed understanding of all the features of the LSC language, the graphical nature of this representation is sufficient to be used as an illustration of the protocol between train and crossing.

Once the activation point is reached, indicated by the second row in the LSC header, the train activates the crossing. The activation point is the latest point at which the train can initiate the securing of the crossing, if it is to be passed without braking. In the hard-wired control this point was given by a fixed sensor, which sent a signal to the crossing. In the radio-based version this point can be determined dynamically. The exact position of this point must consider the delays for communication setup, message transmission, the time necessary to secure the crossing, an additional safety interval and the speed and position of the train. The crossing acknowledges the receipt of the activation request and starts the securing procedure by switching on first the yellow and then the red light of the traffic lights in order to warn the car traffic. Then the command to close the barriers is given and once the barriers are indeed closed, the crossing is in a secured state.

After the amount of time has passed, which in ordinary circumstances is needed to secure the crossing, the train requests a status report from the crossing. Here, the crossing responds with the report *safe*. Should the crossing not be in a safe state when the status request arrives, no response is given. In the hard-wired control this corresponds to the crossing setting the guarding signal to *go* in the safe case, and leaving it set to *stop* in the unsafe case.

A pass sensor determines when the train has passed the crossing and sends a corresponding signal to the crossing controller. Then the crossing is returned into its normal state, i.e. the barriers are opened again and the traffic lights are switched off.

Before a train can approach and contact a crossing, it needs to know the position of the crossing. This information is stored in a *track chart* along with other details about the track, like maximal velocity, position of crossings, points, stations, etc. Once the train has been granted movement authorization for a track segment, it looks up the relevant information in the track chart and places *control points* at all potentially dangerous points, which can e.g. be track segments with a lowered maximally allowed speed, crossings, points, stations, or the end of the assigned track segment. With each control point a target speed is associated, which must be observed; for not secured crossings or not set points for instance this speed is zero, so that the train e.g. has to stop in front of a crossing. Control points due to crossings, points, stations or the end of the assigned track segment require some action on the part of the train: a crossing needs to be secured before it can be passed, a switch must be set to the right track, the train should stop at a station it is supposed to service, and movement authorization for a subsequent track segment must be requested before reaching the end of the currently assigned segment.

The control points are considered by the train in the calculation of the maximal velocity for each point in time. This speed profile is the basis for the speed supervision, which controls that the train does not go faster than allowed by track, train and control points. Once a control point has become irrelevant, e.g. because a crossing has been secured and it is no longer necessary that the train stops, it is disregarded for the maximal speed computation and thus no longer restricts the train's velocity.

This case study focuses on one aspect of the entire set of tasks necessary for radio-controlled train operation: the control of level crossings. Points, stations, etc. are neglected and it is assumed that movement authorization has been granted. The considered type of crossing guards a single track and its barriers cover only one side of the street.

#### 2.2 STATEMATE Model

The Statemate model of the radio-controlled crossing bases on a model, which has been developed in [KT00], but has been slightly adapted to our needs in this thesis. Earlier versions have been partly described in [DDK99, KM00, DK01]. The model presented here uses the asynchronous simulation semantics of Statemate, a variation using the synchronous semantics exists as well, but is not described in detail here, since the differences are only minor.

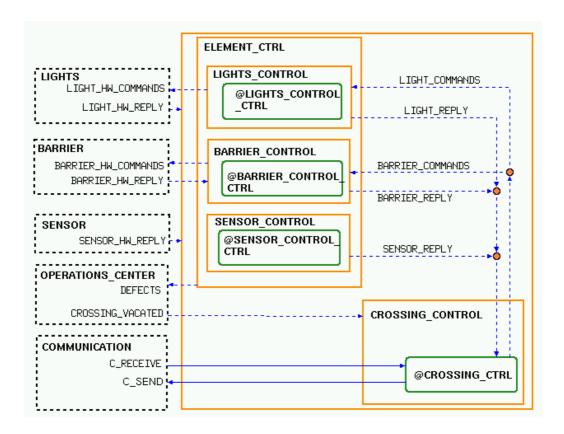

## 2.2.1 Activity Chart SYSTEM

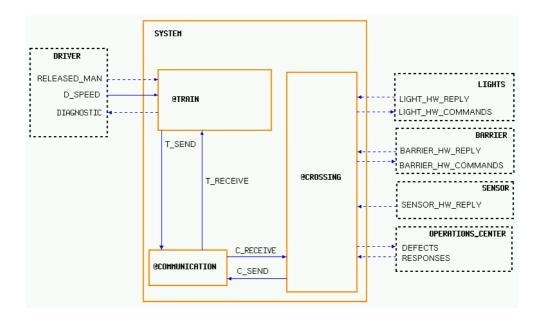

Figure 2.2 on the facing page shows the top level Activity Chart (SYSTEM) of the radio-based crossing control. The two main activities are TRAIN and

Figure 2.2: Top level Activity Chart

CROSSING and the activity COMMUNICATION connecting them. All three internal activities are each further described in a separate Activity Chart as indicated by the '@' in front of the activity name. The environment of the modeled part of the crossing control system is given by the external activities, indicated by the dashed borders. On the train side the environment consists of the console interface to the train driver (activity DRIVER) and on the crossing side there are the sensors and actuators for the peripheral elements. Additionally there is the operation center, to which defect messages are directed and which can send responses to these. The DRIVER determines by D\_SPEED the desired train speed and may re-start the train after an emergency stop by pressing the manual release button (RELEASED\_MAN). The information flow DIAGNOSTIC contains two events for the indication of the train stopping in front of a not secured crossing and for the passing of the crossing, respectively.

The activity TRAIN (cf. section 2.2.2 on the next page) implements only those parts of the train, which are necessary for the protocol considered here. These are the control of the speed and applying the brake if needed, the odometer for keeping track of the position and speed, and the major task: the activation of the crossing.

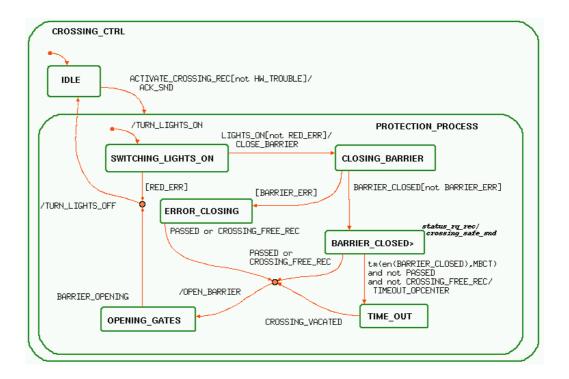

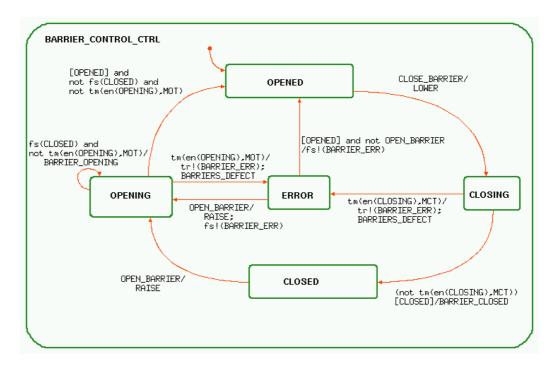

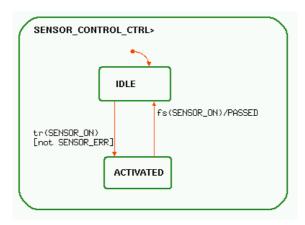

The implementation of a crossing in activity CROSSING (cf. section 2.2.4 on page 37) contains sub-controllers for all peripheral elements (lights, barrier, pass sensor) as well as the overall control for securing the crossing.

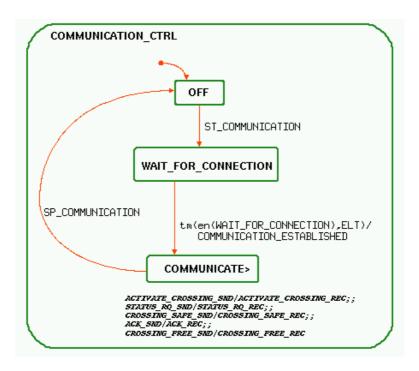

The information flow between TRAIN and CROSSING is established by means of activity COMMUNICATION (cf. section 2.2.3 on page 36). The information exchange takes place via the information flows T\_SEND and T\_RECEIVE between TRAIN and COMMUNICATION, respectively C\_SEND and C\_RECEIVE between CROSSING and COMMUNICATION. The signals sent in T\_SEND and C\_SEND are relayed by COMMUNICATION to the corresponding receive channel (C\_RECEIVE, resp. T\_RECEIVE). The exact contents of information flows is listed in appendix B.

### 2.2.2 Activity Chart TRAIN

Figure 2.3: Activity Chart TRAIN

The train consists of several sub-components as shown in figure 2.3. The activity TRAIN\_CTRL forms the core of the train comprising the two functionalities of communication with the crossings (ACTIVATE\_CROSSING) and supervising the train's speed (SPEED\_CONTROL). The activity ODOMETER keeps track of the train's speed and position and the BRAKE slows down the train, if necessary.

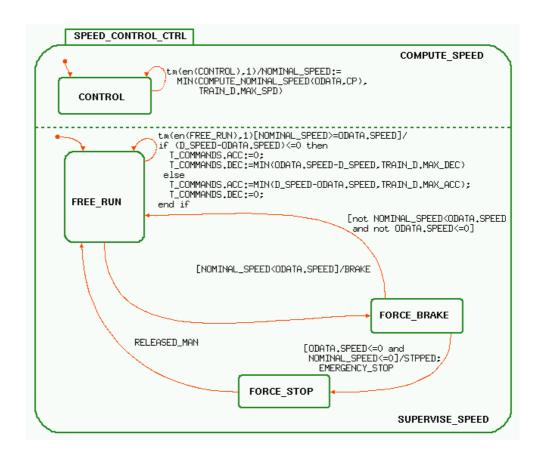

### Statechart SPEED\_CONTROL\_CTRL

The behavior of activity SPEED\_CONTROL is described by Statechart SPEED\_CONTROL\_CTRL shown in figure 2.4, which consists of two parallel sub-states: COMPUTE\_SPEED computes the maximally allowed speed (NOMINAL\_SPEED), whereas SUPERVISE\_SPEED checks if the current train speed is below the maximum.

The computation of the NOMINAL\_SPEED is done every super-step utilizing a timeout event and the implicit entered event for state CONTROL: en(CONTROL). The actual computation is done by function COMPUTE\_NOMINAL\_SPEED, which takes the dynamic train data (ODATA) and the next control point (CP) as parameters. A control point may be set, i.e. it must be observed and the target speed at its position is thus zero, or deleted, i.e. it need not be observed any more and the target speed at its position is set to the maximal value for this track segment. All control points in a track segment are set by default when movement authorization is granted to the train for this segment.

The function COMPUTE\_NOMINAL\_SPEED checks, if control point CP still needs to be observed and if so, determines the maximal speed depending on the train's current distance to the control point:

```

if CP.ALREADY_REGARDED==true then

RET:=30

else

if TRAIN.POS>=CP.POS then

RET:=0

else

DIST:=CP.POS-TRAIN.POS;

if DIST<=10 then RET:=0

else if DIST<=30 then RET:=5

else if DIST<=50 then RET:=10

else

if DIST<=80 then RET:=20

else RET:=30

end if

end if

end if

end if

```

end if

end if;

return(RET)

Figure 2.4: Statechart SPEED\_CONTROL

The resulting speed is the maximal speed for the current position and can not be larger than the maximal speed allowed for this track segment. Taking the minimum of the computed value and the train's maximal speed yields the overall maximal speed NOMINAL\_SPEED.

The lower sub-state checks if the current train speed (ODATA.SPEED) is within the allowed range. If so, the Statechart stays in state FREE\_RUN and computes the new acceleration and deceleration values depending on the speed set by the driver (D\_SPEED). This adjustment is performed by the self loop on FREE\_RUN as long as the train does not exceed its allowed speed

as computed by sub-state COMPUTE\_SPEED (condition part of the transition annotation of the self loop). The implemented algorithm is fairly simple: If the speed set by the driver is lower than the current train speed, the train is decelerated by the difference, otherwise it is accelerated. If the two speeds are equal, the train is neither accelerated nor decelerated.

If the train speed is greater than the allowed speed, state FREE\_RUN is exited, FORCE\_BRAKE is entered and the brake is activated. Once the speed is less than the maximal speed again and the train has not stopped, the State-chart returns to FREE\_RUN. If the NOMINAL\_SPEED and the actual train speed are both zero, the train has stopped in front of a still active control point, state FORCE\_STOP is entered and SPEED\_CONTROL\_CTRL emits the event STPPED to ACTIVATE\_CROSSING\_CTRL and EMERGENCY\_STOP to the driver. Note that only those stops are covered by STPPED, which result from NOMINAL\_SPEED dropping to zero. If the train stops for other reasons, it may resume its course on its own without intervention by the driver. In the former case, however, the driver has to manually confirm that the crossing may be passed safely (RELEASE\_MAN) in order to continue. SPEED\_CONTROL\_CTRL then switches back into the normal behavior of state FREE\_RUN.

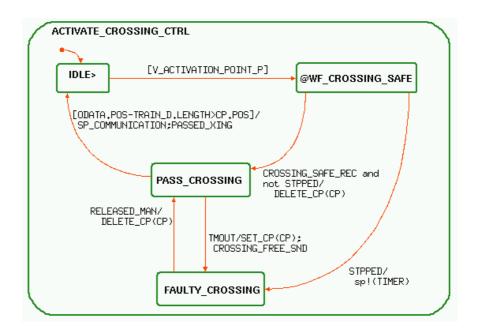

### Statechart ACTIVATE\_CROSSING\_CTRL

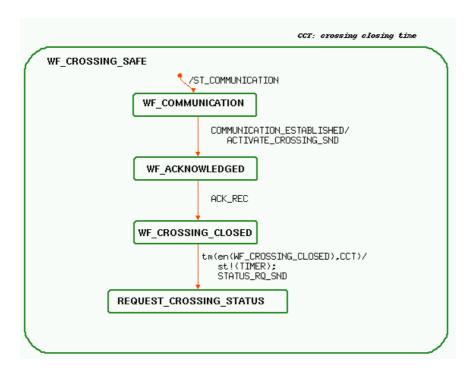

The activity ACTIVATE\_CROSSING (cf. figure 2.3 on page 28) contains the Statechart ACTIVATE\_CROSSING\_CTRL shown in figure 2.5 on the next page, which handles the communication between train and crossing, and a timer, which is used to supervise that the train reaches a secured crossing in time. The communication behavior of the train is described by ACTIVATE\_CROSSING\_CTRL. Once the train reaches the activation point — indicated by the condition V\_ACTIVATION\_POINT\_P<sup>1</sup> — it changes its state from IDLE to WF\_CROSSING\_SAFE, which realizes both the setup of the communication channel and the protocol between the train and the crossing. The detailed behavior is shown in Statechart WF\_CROSSING\_SAFE in figure 2.6.

On entering WF\_CROSSING\_SAFE the communication channel with the crossing is setup. Once the connection has been established, the train requests the securing of the crossing by emitting the event

<sup>&</sup>lt;sup>1</sup>Note that the conditions marked by the suffix \_P represent procedures, which are not included in the model. The conditions thus represent the result of the procedures. Condition V\_ACTIVATION\_POINT\_P abstracts from the computation of the activation point for a crossing.

Figure 2.5: Statechart Activate\_Crossing

ACTIVATE\_CROSSING\_SND. On receiving the acknowledgment from the crossing (ACK\_REC), the train sends the status request (STATUS\_RQ\_SND) after waiting for the amount of time needed by the crossing to carry out the securing procedure. This is the crossing closing time CCT. Simultaneously with the status request a timer is started, which supervises that the train reaches the crossing in time (see below). In the last state of WF\_CROSSING\_SAFE the status message of the crossing is awaited.

Returning to ACTIVATE\_CROSSING\_CTRL, first the normal case is considered, i.e. the report indicates a successful securing of the crossing (CROSSING\_SAFE\_REC). State PASS\_CROSSING is entered and the control point is deleted by function DELETE\_CP. When the train now passes the crossing — represented by its control point — the communication channel is closed (SP\_COMMUNICATION) and the train is ready for the next crossing.

During the securing procedure two error situations can arise: First, there may be problems at the crossing, so that it is not in a safe state when the status request arrives. In this case it does not answer and therefore the train cannot delete the control point with the result that it stops in front of the crossing. This is indicated by Statechart SPEED\_CONTROL\_CTRL

Figure 2.6: Statechart WF\_CROSSING\_SAFE

with the event STPPED triggering the transition from WF\_CROSSING\_SAFE to FAULTY\_CROSSING. Since the train has stopped already, the timer becomes irrelevant and is stopped. In this situation the driver has to manually confirm that the crossing can be safely passed (RELEASE\_MAN) entering state PASS\_CROSSING and deleting the control point in order to allow the train to pass it.

The second error situation arises when the crossing has answered the status request but the train is unable to pass it within the maximal barrier closed time. This is indicated by the event TMOUT sent by the timer resulting in changing from state PASS\_CROSSING to FAULTY\_CROSSING, setting the control point again via the function SET\_CP and notifying the crossing that the train will not reach it in time (event CROSSING\_FREE\_SND). Again this situation has to be resolved by the driver.

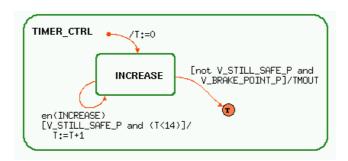

Figure 2.7: Statechart TIMER\_CTRL

### Statechart TIMER\_CTRL

The timer depicted by Statechart TIMER\_CTRL<sup>2</sup> in figure 2.7 supervises that the train reaches an already secured crossing before the maximal barrier closed time elapses, i.e. the maximum amount of time that a crossing may stay closed without a train passing it. The reason for this upper limit is that car drivers tend to become impatient, if no train passes after some time, and start to drive around the barriers<sup>3</sup>, which creates a highly dangerous situation. A timeout (TMOUT) is generated when this property is violated.

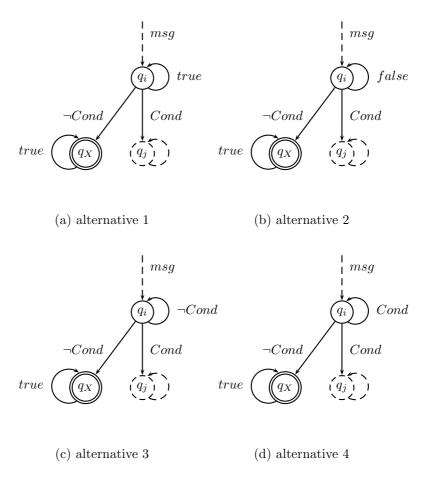

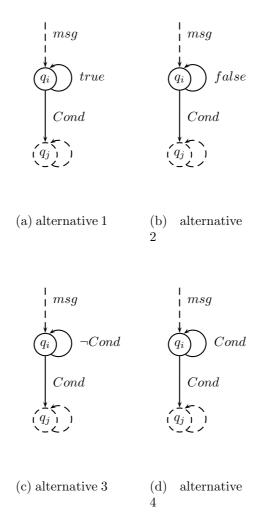

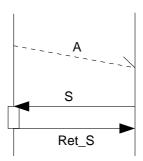

The timer implements a simple counter which increments counter variable T. The timeout is generated depending on two conditions, V\_STILL\_SAFE\_P and V\_BRAKE\_POINT\_P, which again represent the result of procedures: